# Graphics Client Plus User's Manual

ADS document # 110110-8001B

# **Applied Data Systems**

www.applieddata.net

9140 Guilford Road Columbia MD 21046 301-490-4007

© 2001 ADS

# **Revision History**

ADS document # 110110-8001B.

| REV | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | DATE    | BY |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|----|

| 1   | First release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4/13/00 | ak |

| 2   | Corrections on J7 Correct mating headers for Molex 2, 4 & 6-pin Update cover image, block diagram and mechanical drawing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5/11/00 | ak |

| A   | Update for rev B boards (esp. JP7) Restructure Getting Started section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 6/1/00  | ak |

| В   | Add cover photo information Correct reversal of JP2 and JP3 descriptions Apply consistent usage of ADSmartIO <sup>TM</sup> Add signal descriptions, 4.8.4 "LCD Panel" Add note on voltage limits of VPERM (4.3.3) Add more information about power management in section 4.6. Clarify how to enable ADSmartIO <sup>TM</sup> software pull-ups in section 4.8.1 Add details about StrongARM <sup>TM</sup> digital I/O lines in section 4.8.3 Add table in section 3.7.14 that matches ADS signal names to StrongARM <sup>TM</sup> signal names, and add notes about creating panel cables Add diagrams of location of each jumper and signal connector. Update description of J9 Add PCMCIA mating ejector part number Correct error in polarity of J13-5 for LS520 backlight inverter Update ADS logo Add notes on EMI/RFI | 3/21/01 | ak |

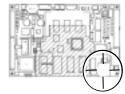

# **About the Cover Photo**

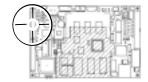

The cover photo shows a fully-populated Graphics Client Plus with 32MB of SDRAM and 32MB of onboard flash. The IrDA option is not shown populated.

(This page intentionally blank)

# **Table of Contents**

| Revision | n History                                    | 1   |

|----------|----------------------------------------------|-----|

| About th | he Cover Photo                               | i   |

| Table of | f Contents                                   | iii |

| 1        | Introduction                                 | 1   |

|          | 1.1 Overview                                 | 1   |

|          | 1.2 What's New for the Graphics Client Plus? |     |

|          |                                              |     |

|          | 1.3 Features                                 |     |

|          | 1.3.2 Memory                                 |     |

|          | 1.3.3 Communications                         |     |

|          | 1.3.4 Interface/Display                      | 2   |

|          | 1.4 Block Diagram                            | 2   |

| 2        | Getting Started                              | 3   |

|          | 2.1 Evaluation Systems                       | 3   |

|          | 2.2 Frequently Asked Questions               | 3   |

|          | 2.3 Organization of this Manual              | 4   |

|          | 2.4 For Further Information                  | 4   |

| 3        | Hardware Reference                           | 5   |

|          | 3.1 Locating "Pin 1"                         | 5   |

|          | 3.2 Switches                                 | 5   |

|          | 3.2.1 SW1: Reset Switch                      |     |

|          | 3.3 Potentiometers                           |     |

|          | 3.3.1 VR1: Contrast Adjustment               | 5   |

|          | 3.3.2 VR2: Passive Panel Voltage Adjustment  |     |

|          | 3.4 ADSmartIO <sup>TM</sup>                  |     |

|          | 3.5 Onboard LEDs                             | 6   |

|          | 3.6 Jumper Settings                          | 6   |

|          | 3.6.1 JP1: Flat Panel Voltage Select         | 6   |

|          | 3.6.2 JP2: Panel RL                          | 6   |

|          | 3.6.3 JP3: Panel UD                          | 6   |

|   | 3.6.4 JP3: Source of Steep Mode Power                      |    |

|---|------------------------------------------------------------|----|

|   | 3.6.5 JP6: Onboard 3.3V Converter Select                   |    |

|   | 3.6.6 JP7: Serial Port 2 Mode Select                       |    |

|   | 3.6.7 JP8 to JP11, JP14 to JP15: Serial Port 1 Mode Select | 8  |

|   | 3.6.8 JP12: Flat Panel Vee (Contrast) Adjust Mode          | 8  |

|   | 3.6.9 JP13: Flat Panel Data Voltage Select                 | 9  |

|   | 3.6.10 JP16: DCD-DTR loopback                              |    |

|   | 3.6.11 JP17: DSR-DTR loopback                              | g  |

|   | 3.6.12 J19: Flat Panel Vee Select                          | 9  |

|   | 3.7 Connector Pinouts                                      | 1( |

|   |                                                            |    |

|   | 3.7.1 J1: Contact Closure Detect                           |    |

|   | 3.7.2 J2: USB, A/D, Digital I/O                            |    |

|   | 3.7.3 J3: Battery Connector                                |    |

|   | 3.7.4 J4: Touch Panel                                      |    |

|   | 3.7.5 J5: Power Input                                      |    |

|   | 3.7.6 J6: PS/2 Keyboard Input                              |    |

|   | 3.7.7 J7: Serial Ports 1 & 2, Matrix Keypad, Power Outputs |    |

|   | 3.7.8 J8: Ethernet                                         |    |

|   | 3.7.9 J9: Manufacturing Test                               | 14 |

|   | 3.7.10 J10: Serial Port 3                                  | 15 |

|   | 3.7.11 J11: PCMCIA                                         | 15 |

|   | 3.7.12 J12: Flat Panel (Hirose connector)                  | 16 |

|   | 3.7.13 J13: Backlight Inverter                             | 17 |

|   | 3.7.14 J14: Flat Panel (IDC 34)                            | 18 |

|   | 3.7.15 J15: Manufacturing Test                             | 19 |

|   | 3.7.16 J16: Speaker                                        | 20 |

|   | 3.7.17 J17: Microphone                                     | 20 |

|   | 3.7.18 J18: CAN Bus                                        | 20 |

| 4 | System Integration                                         | 21 |

|   | .,                                                         |    |

|   | 4.1 Tips for System Integration                            | 21 |

|   | 4.1.1 Strategies for Backup Power                          | 2. |

|   | 4.1.2 Electrical Tips                                      |    |

|   | •                                                          |    |

|   | 4.2 Mechanical Specifications                              | 21 |

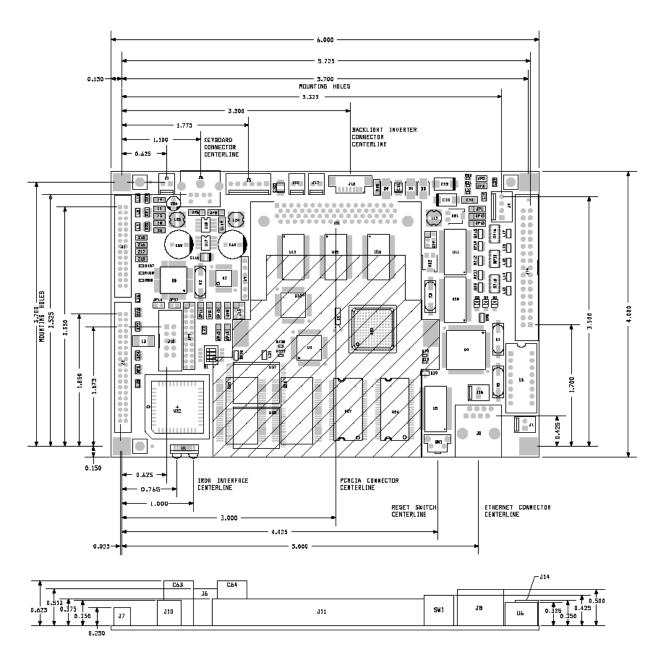

|   | 4.2.1 Mechanical Drawing of Graphics Client Plus           | 21 |

|   | 4.2.2 Mounting Holes                                       |    |

|   | 4.2.3 Clearances                                           |    |

|   | 4.3 Input Power Requirements                               |    |

|   | •                                                          |    |

|   | 4.3.1 +5.0V                                                |    |

|   | 4.3.2 +3.3V                                                |    |

|   | 4.3.3 VPERM                                                |    |

|   | 4.3.4 +12V                                                 |    |

|   | 4.3.5 3.0V Battery Backup (J3)                             |    |

|   | 4.3.6 "Power On" Output                                    |    |

|   | 4.3.7 EMI/RFI and Transient Suppression                    | 24 |

|   | 4.4 Externally Available Voltages                          | 24 |

|   | •                                                          |    |

|   | 4.5 Power Consumption                                      | 25 |

|   | A.C. De an Management                                      | 21 |

|   | 4.6 Power Management                                       | 25 |

|   | 4.7 EMI   | /RFI and ESD                        | 25 |

|---|-----------|-------------------------------------|----|

|   | 4.8 Elect | trical Specifications for I/O Ports | 26 |

|   | 4.8.1     | ADSmartIO <sup>TM</sup> Controller  | 26 |

|   |           | UCB 1200                            |    |

|   | 4.8.3     | SA-1110                             | 27 |

|   | 4.8.4     | LCD Panel                           | 27 |

| 5 | Board Rev | rision History                      | 29 |

|   | 5.1.1     | Identifying the board revision      | 29 |

|   |           | Revision History                    |    |

(this page intentionally blank)

## 1 Introduction

#### 1.1 **Overview**

The Graphics Client Plus is a full-featured single board computer using the SA-1110 StrongARM<sup>TM</sup> RISC microprocessor. The Graphics Client Plus is designed to meet the needs of embedded and graphical systems developers.

## 1.2 What's New for the Graphics Client Plus?

The Graphics Client Plus adds to the successful design of the Graphics Client with the following new features:

- StrongARM<sup>TM</sup> SA-1110 processor

- Synchronous DRAM (4x memory bus performance)

- CAN bus controller with connector J18

- Supports both 5V and 3.3V PCMCIA cards

- Up to 32MB of flash memory

The following signals have changed on Graphics Client Plus connectors. See the related connector descriptions for details.

- ADSmartIO<sup>TM</sup> line SMTIO4 (J2 pin 20) is now PD0

- ADSmartIO<sup>TM</sup> line SMTIO5 (J2 pin 22) is now PD1

- An external interrupt request input replaces SMTIO6 (J2 pin 24)

- The Serial 3 header (J10) in conjunction with new jumpers JP16 and JP17 allow loopback of external handshaking signals DTR, DSR and DCD.

- Replaced JP4 with J19 to allow +12V as Vee option.

- Panel connector (J14) adds adjustable voltage (pin 34) and panel enable signal (pin 33).

- Backlight control signal (J13 pin 5) now has 12V pull-up.

The board remains a compact 4 by 6 inches. A few minor changes have been made to connector placement. Consult the mechanical drawing in section 4.2.1 for details.

#### 1.3 **Features**

#### 1.3.1 Processor

- SA-1110 32-bit StrongARM<sup>TM</sup>

- Clock rates up to 206 MHz

#### 1.3.2 Memory

- 16, 32or 64 MB synchronous DRAM (1/2 of CPU clock)

- 8. 16 or 32 MB Flash

- 3.3 and 5V PCMCIA

## 1.3.3 Communications

• Ethernet, RJ45

CAN bus

• Three Serial: IrDA, RS-232, RS-422, RS-485 and CMOS available

Serial 1: RS-232, RS-422 or RS-485 Serial 2: RS-232, 3.3V CMOS or IrDA

Serial 3: RS-232

# 1.3.4 Interface/Display

- Flat panel interface

- Analog touch panel interface

- PS/2 keyboard interface

- Four 10-bit analog inputs

- Contact closure detection

- ADSmartIO<sup>TM</sup>

Configurable for digital I/O, PWM and A/D inputs

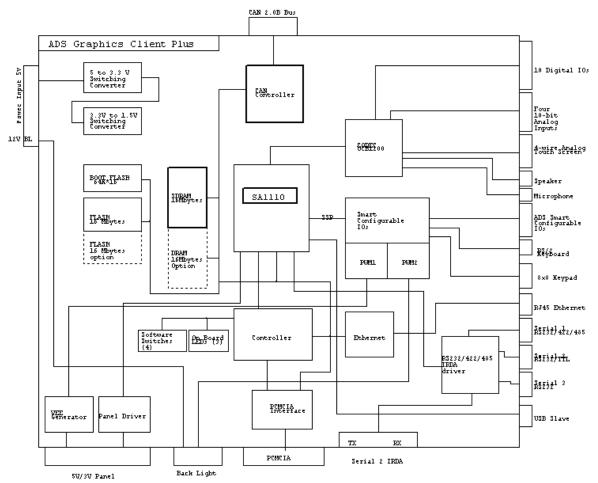

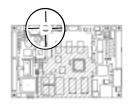

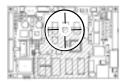

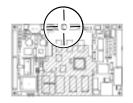

# 1.4 Block Diagram

The following diagram illustrates the system organization of the Graphics Client Plus.

# 2 Getting Started

## 2.1 Evaluation Systems

Graphics Client Plus boards are shipped as evaluation systems designed to get the developer up and running quickly.

#### To use the system, simply plug power supply into the mini DIN-8 receptacle on the system.

If the screen does not display anything after five to ten seconds, check the *Frequently Asked Questions*, below. Most operating systems cold boot within twenty seconds.

An evaluation system consists of the following:

- Graphics Client Plus single-board computer

- Flat panel display and cable

- Backlight inverter

- Touch screen and cable

- 120VAC power supply

- Plexiglas mounting

- Developer's Cable Kit

- Operating system of your choice

- User's Guide (this document and operating system guide)

# 2.2 Frequently Asked Questions

The following are some of the most commonly asked questions for evaluation systems:

#### Q: When I turn on power, my screen is white and nothing comes up on it.

A: Check the connector seating. The flat panel connector may have come loose in shipping. Press it firmly into the panel and reapply power to your system.

#### Q: What does the pushbutton do?

A: The push button (SW1) issues a hard reset to the processor, which restarts the real-time clock and may clear memory (RAM). Your application will most likely leave the system in sleep mode when not in use, so this button will rarely be used by your customers.

#### Q: Do I have to turn off the system before I insert a PCMCIA card?

A: No. The Graphics Client Plus supports hot-swapping of PCMCIA cards.

#### Q: Do I need to observe any ESD precautions when working with the system?

A: Yes. If possible, work on a grounded anti-static mat. At a minimum, touch an electrically grounded object before handling the board or touching any components on the board.

#### Q: What do I need to start developing my application for the system?

A: You will need a flash ATA card (8MB or larger) and the cables supplied with your system to interface your development station to the system. For further direction, consult the ADS guide for the installed operating system.

#### Q: Who can I call if I need help developing my application?

A: ADS provides technical support to get your development system running. For customers who establish a business relationship with ADS, we provide support to develop applications and drivers.

#### Q: Can I upgrade the version of the operating system?

A: Yes. ADS provides regular operating system updates on its developers' web site. For operating systems not maintained by ADS, contact the operating system vendor.

#### Q: Can I order a bare board?

A: It takes a significant effort to build the cables and drivers for a complete system. For support reasons, ADS only ships bare boards to customers to whom it has shipped functioning evaluation systems and with whom it has an established business relationship.

#### Q: I would like to interface to a different display panel. How can I do this?

A: ADS may have already interfaced to the panel you are interested in. Consult ADS for availability. ADS can interface to just about any panel you provide.

## 2.3 Organization of this Manual

The manual organizes information in three key sections:

**Introduction** Provides an overview of the functionality and organization of the

Graphics Client Plus.

**Hardware Reference** Describes the configuration settings and connector pinouts for all

systems of the Graphics Client Plus.

**System Integration** Provides key information about power management, tips for system

integration and electrical and mechanical interface specifications.

To locate the information you need, try the following:

Browse the *Table of Contents*. Section titles include connector designators and their function.

- 2. Follow cross-references between sections.

- 3. View and search this manual in PDF format

#### 2.4 For Further Information...

ADS maintains a web site exclusively for its developers. The site includes downloads, troubleshooting guides, operating system updates and the "ADS Knowledge Base", a comprehensive document with dozens of questions answered about developing applications for ADS products. Instructions on how to access the site are shipped with every evaluation system.

## 3 Hardware Reference

This section gives an overview of the hardware features of the Graphics Client Plus. This overview includes a description of the switches, jumper settings, connector and connector pinouts.

#### 3.1 **Locating "Pin 1"**

Many connectors and headers have a visible number on the board that indicates pin 1. If that pin is not clearly marked, there are two other ways to locate pin 1:

- 1. The easiest method is to look at the underside of the board. The square pad is pin 1.

- 2. You can determine pin 1 from the mechanical drawing provided in section 4.2.1.

#### 3.2 **Switches**

#### 3.2.1 SW1: Reset Switch

SW1 is the reset switch for the Graphics Client Plus. This switch issues a hardware reset to the SA-1110. Press this button to restart the Graphics Client Plus without cycling power. This operation will reset the real-time clock. Most operating systems clear the contents of DRAM upon hardware reset.

You can hold the Graphics Client Plus in reset by pressing and holding this button.

#### 3.2.2 S1: DIP Switch

S1 is a four-position DIP switch. It connects to the controller CPLD. The settings of individual switches can be read from the controller. Some operating systems on the Graphics Client Plus reserve these switches for their use. Consult the operating system manual for details.

#### 3.3 **Potentiometers**

# 3.3.1 VR1: Contrast Adjustment

You can adjust Vee (panel contrast) with the single-turn potentiometer VR1 on boards that have the Vee option installed. You may also control Vee through software with the ADSmartIO<sup>TM</sup> controller. See J19, JP12 and you operating system reference for further details.

#### 3.3.2 VR2: Passive Panel Voltage Adjustment

You can adjust the VCON voltage on J14 pin 33 with the single-turn potentiometer VR2 on boards that have that option installed. This potentiometer may be replaced by fixed resistors or not installed at all in some Graphics Client Plus configurations.

# 3.4 **ADSmartIO**<sup>TM</sup>

ADSmartIO<sup>TM</sup> ports are available on J2 and J7. The ADSmartIO<sup>TM</sup> ports are flexible and can be configured through software. Consult your operating system reference guide for the Graphics Client Plus for details.

#### 3.5 **Onboard LEDs**

The Graphics Client Plus has three onboard LEDs. They are mapped as follows:

| Signal  | GPIO line | Part Designator | Color |

|---------|-----------|-----------------|-------|

| LEDOUT0 | 20        | D3              | Green |

| LEDOUT1 | 21        | D2              | Amber |

| LEDOUT2 | 22        | D1              | Red   |

# 3.6 **Jumper Settings**

Jumpers on the Graphics Client Plus select a variety of operational options. All use 2mm shorting blocks (shunts) to select settings. Make sure power is turned off to the Graphics Client Plus when changing the position of a shorting block. Diagrams indicate location of the jumpers.

# 3.6.1 JP1: Flat Panel Voltage Select

This jumper selects the supply voltage for the flat panel. The voltage selected here is passed to the *PNL\_PWR* connection (pins 28 and 29) on J12.

| Jumper setting | Voltage Selected |

|----------------|------------------|

| 1-2            | 3.3 V            |

| 2-3            | 5.0 V            |

WARNING! Make sure you have selected the correct voltage before connecting the panel. Flat panels are sensitive to--and are often irreparably damaged by--incorrect voltages.

#### 3.6.2 JP2: Panel RL

Type: 2-post header, 2mm

On some active flat panel displays, this signal flips the displayed image right-to-left.

| Jumper settings | Connect RL to |

|-----------------|---------------|

| 1-2             | Ground        |

| none            | PNL_PWR       |

#### 3.6.3 JP3: Panel UD

Type: 2-post header, 2mm

On some active flat panel displays, this signal flips the displayed image bottom-to-top.

| Jumper setting | Connect UD to |

|----------------|---------------|

| 1-2            | Ground        |

| none           | PNL_PWR       |

## 3.6.4 JP5: Source of Sleep Mode Power

Type: 3-post header, 2mm

This jumper selects the source of power to back up the Graphics Client Plus when it is in sleep mode. See J5 for further details.

| Jumper setting | Power supplied by |

|----------------|-------------------|

| 1-2            | VPERM             |

| 2-3            | VCC (+5V_IN)      |

# 3.6.5 JP6: Onboard 3.3V Converter Select

Type: 3-post header, 2mm

This jumper selects between an external 3.3V supply (+3.3V\_IN) and the onboard 3.3V supply (+3.3VINT), if installed. The onboard supply is installed as an option on the Graphics Client Plus. J5 is the source of the external 3.3V supply.

| Jumper setting | +3.3V connected to  |

|----------------|---------------------|

| 1-2            | +3.3V_IN (external) |

| 2-3            | +3.3VINT (internal) |

#### 3.6.6 JP7: Serial Port 2 Mode Select

Type: 2x12 header, 2mm

This header selects the communications mode of Serial Port 2 of the SA-1110. Odd-numbered pins are on the side closer to the outer edge of the Graphics Client Plus. Pins 1 and 2 are closest to U7.

The operating system must configure the processor for the target serial mode. The table below lists the standard voltages to expect on the transmit line of the port when the transmitter is idle.

Important: When using Serial 2 as IrDA, make sure that the operating system configures the port as IrDA. Otherwise, the transmitter may be turned on continuously, which will drain significant amounts of power and may damage IrDA transmitter.

| Serial 2 Mode | JP7 Shunt Settings<br>(Rev B <sup>1</sup> )      | Tx V <sub>idle</sub> |

|---------------|--------------------------------------------------|----------------------|

| RS-232        | 1-2, 3-4, 5-6, 7-8, 9-10,<br>15-16, 17-18, 23-24 | -6 V                 |

| 3.3V CMOS     | 1-3, 5-7<br>13-14, 21-22                         | 3.3 V                |

| IrDA          | 11-12, 19-20                                     | 0 V                  |

<sup>&</sup>lt;sup>1</sup> Note: Serial Port 2 on Revision A Graphics Client Plus boards is factory wired for a single mode of operation. Jumper wires and shunt settings for Rev. A boards are shown below.

| Serial 2 Mode | Rev A JP7 Shunt Settings (jumper wires)           |

|---------------|---------------------------------------------------|

| RS-232        | 1-2, 3-4, 5-6, 7-8, 15-16, 23-24, (9-18), (10-17) |

| 3.3V CMOS     | 1-3, 5-7, (13-22), (14-21)                        |

| IrDA          | (12-19), (11-20)                                  |

# 3.6.7 JP8 to JP11, JP14 to JP15: Serial Port 1 Mode Select

Type: 3-post headers, 2mm

Jumpers JP8 through JP11 select between RS-232 and RS-485/422 mode and set the duplex mode of RS-485/422.

RS-422 and RS-485 are differential serial protocols with the same voltage characteristics. RS-422 is a point-to-point protocol while RS-485 turns off the transmitter when not in use, allowing multi-drop installations. Each can be configured in half- or full-duplex mode. The Graphics Client Plus supports RS-422 by leaving the transmitter enabled all the time.

In half-duplex mode, TX+/RX+ and TX-/RX- are shorted together. Half-duplex devices can see their own transmissions. Connect to either the + or - connection on J7, but make sure to observe correct polarity.

For diagnostic purposes, RS-485/422 signals are available on jumper pins as follows: JP8.1 TX+, JP8.2 RX+, JP11.1 TX-, JP11.2 RX-.

The following table indicates shunt settings for each mode of Serial Port 1:

| Mode                                     | J          | umper     | Settin               | g                         |

|------------------------------------------|------------|-----------|----------------------|---------------------------|

| RS-232                                   | JP10       | JP9       | JP8 1 2 3 1 2 3 JP15 | JP11 12 3 12 3 JP14       |

| RS-485/422<br>Half Duplex<br>(two-wire)  | JP10       | JP9 1 2 3 | JP8 12 3 JP15        | JP11 1 2 3 1 1 2 3 1 JP14 |

| RS-485/422<br>Full Duplex<br>(four-wire) | JP10 1 2 3 | JP9 1 2 3 | JP8 1 2 3 1 2 3 JP15 | JP11 1 2 3 1 2 3 JP14     |

# 3.6.8 JP12: Flat Panel Vee (Contrast) Adjust Mode

Type: 3-post header, 2mm

Selects if panel Vee will be adjusted electronically or manually. Vee determines the contrast for some panels. The polarity of Vee is set by J19.

| Jumper setting | Voltage Selected                                               |

|----------------|----------------------------------------------------------------|

| 1-2            | Vee adjusted by PWM from<br>ADSmartIO <sup>TM</sup> controller |

| 2-3            | Adjust voltage with potentiometer VR1                          |

# 3.6.9 JP13: Flat Panel Data Voltage Select

Type: 3-post header, 2mm

This jumper selects the voltage of the data lines for the flat panel display.

Important: These jumpers are set at the factory to match the panel and drivers shipped with the system. They should not be changed by the user. You may damage the panel or panel drivers if you change this jumper setting.

Tip: Most 5V panels will run correctly with 3.3V data.

| Jumper setting | Voltage Selected |

|----------------|------------------|

| 1-2            | 3.3 V            |

| 2-3            | 5.0 V            |

# 3.6.10 JP16: DCD-DTR loopback

Type: 2-post header, 2mm

This jumper allows loopback of the DCD and DTR signals, if they are present on the external device connected to J10. This jumper and JP17 can create a null modem connection for some serial connections.

| Jumper setting | Function                   |

|----------------|----------------------------|

| 1-2            | shorts pins 1 and 7 of J10 |

# 3.6.11 JP17: DSR-DTR loopback

Type: 2-post header, 2mm

This jumper allows loopback of the DSR and DTR signals, if they are supplied by the external device connected to J10. This jumper and JP16 can create a null modem connection for some serial connections.

| Jumper setting | Function                   |

|----------------|----------------------------|

| 1-2            | shorts pins 2 and 7 of J10 |

#### 3.6.12 J19: Flat Panel Vee Select

Type: 6-post header, 2mm

This jumper selects the Vee voltage for the flat panel. The source Vee is selected by JP12. You can adjust Vee with VR1 (section 3.3) or through software (JP12, section 3.6.8). Note that Vee is installed only as an option and is not installed on all Graphics Client Plus boards.  $\begin{bmatrix} 1 & 2 \\ 3 & 4 \end{bmatrix}$

| Jumper setting | Voltage Selected |

|----------------|------------------|

| none           | none             |

| 2-4            | Positive Vee     |

| 4-6            | Negative Vee     |

| 3-4            | +12V from J5.4   |

pin numbering

WARNING! Make sure you have selected the correct voltage before connecting the panel. Flat panels are sensitive to--and are often irreparably damaged by--incorrect voltages.

#### 3.7 **Connector Pinouts**

The following tables describe connector pinouts and the type of connector. At least one pin of every connector is labeled on the Graphics Client Plus. Double-row headers on the board are all numbered as shown in the figure to the right.

2 4 6 8 1 3 5 7

For information about the location of the connectors on the Graphics Client Plus, refer to section 4.2, *Mechanical Specifications*:

Legend: n/c Not connected

GND Graphics Client Plus ground plane

#### 3.7.1 J1: Contact Closure Detect

Type: 2-pin header, 0.100-in spacing, friction lock, Molex 22-23-2021

Recommended mating connector: Molex 22-01-3027

External input. Short these pins together to generate a high level on GP1 of the SA-1110. Pin 2 can be used by the application or operating system for user input, contact closure detection or to wake the system from sleep mode.

| Pin | Signal name | Description                                                                  |

|-----|-------------|------------------------------------------------------------------------------|

| 1   | GND         | Ground                                                                       |

| 2   | RQONOFF     | to GP1 of SA-1110 via inverting buffer includes 11k $\Omega$ pull-up to Vddx |

# 3.7.2 J2: USB, A/D, Digital I/O

Type: 2x15 header, 2 mm spacing

Recommended mating connector: TCSD-15 series from SAMTEC

Electrical specifications for signals are referenced in parentheses ().

| Pin | Signal name | Pin | Description              |

|-----|-------------|-----|--------------------------|

| 1   | UCB_IO0     |     |                          |

| 3   | UCB_IO1     |     |                          |

| 5   | UCB_IO2     |     |                          |

| 7   | UCB_IO3     |     | Digital I/Os (10)        |

| 9   | UCB_IO4     |     | Digital 1/0s (10)        |

|     | UCB_IO9     | 2   | (UCB1200, section 4.8.2) |

|     | UCB_IO8     | 4   | (OCD1200, Section 4.0.2) |

|     | UCB_IO7     | 6   |                          |

|     | UCB_IO6     | 8   |                          |

|     | UCB_IO5     | 10  |                          |

| 11  | ANIN0       |     |                          |

| 13  | ANIN1       |     | Analog inputs (4)        |

| 15  | ANIN2       |     | (UCB1200, section 4.8.2) |

| 17  | ANIN3       |     |                          |

| Pin | Signal name | Pin |     | Description                                  |  |  |

|-----|-------------|-----|-----|----------------------------------------------|--|--|

|     | SMTIO0      | 12  | PB0 |                                              |  |  |

|     | SMTIO1      | 14  | PB1 | $ADSmartIO^{TM}$ lines (7)                   |  |  |

|     | SMTIO2      | 16  | PB2 | ADSmarilO lines (7)                          |  |  |

|     | SMTIO3      | 18  | PB3 | (section 4.8.1)                              |  |  |

|     | SMTIO4      | 20  | PD0 | (section 4.0.1)                              |  |  |

|     | SMTIO5      | 22  | PD1 |                                              |  |  |

|     | /EXT_IRQ    | 24  |     | External interrupt 3.3V CMOS with 10k pullup |  |  |

| 19  | UCB_TINP    |     |     |                                              |  |  |

| 21  | UCB_TINN    |     |     | Telecom interface                            |  |  |

| 23  | UCB_TOUTN   |     |     | (UCB1200, section 4.8.2)                     |  |  |

| 25  | UCB_TOUTP   |     |     |                                              |  |  |

|     | USB_VCC     | 26  |     |                                              |  |  |

| 27  | USB_GND     |     | USB |                                              |  |  |

|     | USB_UDC-    | 28  | USB |                                              |  |  |

|     | $USB\_UDC+$ | 30  |     |                                              |  |  |

| 29  | GND         |     |     | Ground                                       |  |  |

# 3.7.3 J3: Battery Connector

Type: 2-pin header, 0.100-in spacing, friction lock, Molex 22-23-2021

Recommended mating connector: Molex 22-01-3027

This connector allows you to connect an external battery to back up power on the Graphics Client Plus. If no other power source is available, the system will draw its sleep mode current (section 4.5) from this connection. There is a steady-state  $1M\Omega$  load across these terminals.

For reliable operation of the Graphics Client Plus, place a 0.100" shunt across the pins of this connector.

| Pin | Signal name | Description                       |

|-----|-------------|-----------------------------------|

| 1   | BATPOS      | 3 Volt battery, positive terminal |

| 2   | BATNEG      | Graphics Client Plus ground       |

#### 3.7.4 J4: Touch Panel

Type: 4-pin header, 0.100-in spacing, friction lock, Molex 22-23-2041

Recommended mating connector: Molex 22-01-3047

The mapping shown of signal to edge of touch panel is an ADS convention. Interface cables are constructed to match this order. Some operating systems can tolerate swapping of positive (P) and negative (M) connections, and even swapping of X and Y pairs.

| Pin | Signal name | Description        |

|-----|-------------|--------------------|

| 1   | TSMX        | Left edge of panel |

| 2   | TSPX        | Right              |

| 3   | TSPY        | Bottom             |

| 4   | TPMY        | Ton                |

## 3.7.5 J5: Power Input

Type: 6pin header, 0.100-in spacing, friction lock, Molex 22-23-2061

Recommended mating connector: Molex 22-01-3067

This connector supplies main and backup power to the Graphics Client Plus. See section 4.3 for additional details about input power requirements.

| Pin | Signal name | Description                                                                                                              |

|-----|-------------|--------------------------------------------------------------------------------------------------------------------------|

| 1   | +5V_IN      | main power: +5 Volts ±5%                                                                                                 |

| 2   | GND_IN      | Ground                                                                                                                   |

| 3   | +3.3V_IN    | $+3.3$ Volts $\pm 5\%$<br>Required if onboard 3.3V supply option is not installed<br>To use, set JP6 to "external 3.3V." |

| 4   | +12V_IN     | For PCMCIA (J11) and backlight (J13)                                                                                     |

| 5   | POWERON     | 3.3V CMOS output; 0V when board power is disabled see section 4.3.6 for further details                                  |

| 6   | VPerm       | 5-12V DC @5mA for sleep mode                                                                                             |

# 3.7.6 J6: PS/2 Keyboard Input

Type: Mini DIN-6 socket housing

Recommended mating connector: PS/2 keyboard

| Pin | Signal name | Description                |

|-----|-------------|----------------------------|

| 1   | SIGPS2      | PS/2 keyboard data         |

| 2   | N/C         | not connected              |

| 3   | GND         | Ground                     |

| 4   | VCC         | + 5 Volts, fused at 350 mA |

| 5   | CLKPS2      | PS/2 keyboard clock        |

| 6   | N/C         | not connected              |

# 3.7.7 J7: Serial Ports 1 & 2, Matrix Keypad, Power Outputs

Type: 2x20 header, 2 mm spacing

Recommended mating connector: TCSD-20 series from SAMTEC

| Pin | Signal name | Pin |     | Description                                    |

|-----|-------------|-----|-----|------------------------------------------------|

| 1   | ROW0        |     | PC7 | ADG JOTM                                       |

| 3   | ROW1        |     | PC6 | ADSmartIO <sup>TM</sup><br>(see section 4.8.1) |

| 5   | ROW2        |     | PC5 | (see section 4.6.1)                            |

| 7   | ROW3        |     | PC4 | Configurable as:                               |

| 9   | ROW4        |     | PC3 | Digital I/O                                    |

| 11  | ROW5        |     | PC2 | Keypad, rows                                   |

| 13  | ROW6        |     | PC1 | ne ypaa, rows                                  |

| 15  | ROW7        |     | PC0 |                                                |

| Pin | Signal name | Pin | Description                             |

|-----|-------------|-----|-----------------------------------------|

|     | RXD2        | 2   | SA-1110 Serial Port 2                   |

|     | TXD2        | 4   | SA-1110 Seriai Pori 2                   |

|     | CTS2        | 6   | RS-232 or CMOS (see JP7)                |

|     | RTS2        | 8   | See also note below                     |

|     | GNDCOM2     | 10  | See also note below                     |

|     | RXD1        | 12  |                                         |

|     | TXD1        | 14  | SA-1110 Serial Port 1                   |

|     | CTS1        | 16  | (see section 3.6.7 and note below)      |

|     | RTS1        | 18  | (see section 5.0.7 and note below)      |

|     | GNDCOM1     | 20  |                                         |

| 17  | COL0        |     | PAO ADSmartIO TM                        |

| 19  | COL1        |     | PA1 (see section 4.8.1)                 |

| 21  | COL2        |     | PA2                                     |

| 23  | COL3        |     | PA3 Configurable as:                    |

| 25  | COL4        |     | PA4 Analog Inputs                       |

| 27  | COL5        |     | PA5 Digital I/O                         |

| 29  | COL6        |     | PA6 Keypad, columns                     |

| 31  | COL7        |     | PA7                                     |

|     | RX422+      | 22  |                                         |

|     | RX422-      | 24  | RS-422/485 lines, Serial Port 1         |

|     | TX422+      | 26  | (see section 3.6.7)                     |

|     | TX422-      | 28  | (see section 5.0.7)                     |

|     | GNDRS422    | 30  |                                         |

|     | GPIO27      | 32  |                                         |

|     | GPIO26      | 34  | SA-1110 GPIOs                           |

|     | GPIO25      | 36  | (see section 4.8.3)                     |

|     | GPIO24      | 38  |                                         |

| 33  | VREF        |     | Voltage reference for ADSmartIO TM A/D; |

| 33  | VKEF        |     | reference use only (<100μA)             |

| 35  | VCC         |     | +5V                                     |

| 37  | +3.3V       |     | +3.3V                                   |

| 39  | GND         |     | Ground                                  |

|     | GND         | 40  | Grouna                                  |

Note: The SA-1110 does not have hardware handshaking on its serial lines. The Graphics Client Plus is wired to use SA-1110 GPIO lines to perform CTS/RTS handshaking as follows:

| SA-1110 | Function |           |  |

|---------|----------|-----------|--|

| GPIO    | RS-232   | RS-485    |  |

| 14      | CTS1     | RX enable |  |

| 15      | RTS1     | TX enable |  |

| 16      | CTS2     |           |  |

| 17      | RTS2     |           |  |

| 18      | CTS3     |           |  |

| 19      | RTS3     |           |  |

# 3.7.8 J8: Ethernet

Type: RJ-45 socket

Recommended mating connector: RJ-45 plug.

Connects to the onboard Ethernet driver.

| Pin | Signal name | Description   |

|-----|-------------|---------------|

| 1   | ETHP1       | Transmit +    |

| 2   | ETHP2       | Transmit -    |

| 3   | ЕТНР3       | Receive +     |

| 4   | n/c         | not connected |

| 5   | n/C         | noi connectea |

| 6   | ЕТНР6       | Receive -     |

| 7   | n/c         | not connected |

| 8   | n/C         | noi connectea |

# 3.7.9 J9: Manufacturing Test

Type: 6-pin header, 1x6 0.100-inch spacing.

For manufacturing use.

#### 3.7.10 J10: Serial Port 3

Type: 2x5 header, 0.100" IDC, keyed

Recommended mating connector: 2x5 IDC

| Pin | Signal name | Description                                                        |  |

|-----|-------------|--------------------------------------------------------------------|--|

| 1   | "DCD3"      | DCD from external device see JP16 for loopback options             |  |

| 2   | "DSR3"      | DSR from external device<br>see JP17 for loopback options          |  |

| 3   | RXD3        |                                                                    |  |

| 4   | RTS3        | SA-1110 Serial Port 3, RS-232                                      |  |

| 5   | TXD3        | 5A-1110 Seriai 1 011 5, K5-252                                     |  |

| 6   | CTS3        |                                                                    |  |

| 7   | "DTR3"      | DTR from external device<br>see JP16 and JP17 for loopback options |  |

| 8   | n/c         | not connected                                                      |  |

| 9   | GNDFILT3    | filtered connection to ground                                      |  |

| 10  | n/c         | not connected                                                      |  |

Note: The SA-1110 does not have hardware handshaking on its serial lines. The Graphics Client Plus is wired to use SA-1110 GPIO lines to perform CTS/RTS handshaking. See the table on page 13 for port assignments.

#### 3.7.11 J11: PCMCIA

Type: Type II, 5V PCMCIA header

Mating ejector Amp #146019-1 available in production systems

The PCMCIA socket conforms to the PCMCIA standard for 5V and dual-voltage Type II cards. It will supply up to 500 mA of 5V or 3.3V current. The socket is normally de-energized; the operating system is responsible for turning on the socket when a card is inserted and turning it off when the card is removed.

Note:  $V_{PP}$  (pins 18 and 52) is supplied from the "+12V" input (pin 4 on J5). Since few PCMCIA cards manufactured use this voltage, most applications can set the J5.4 input voltage to match the backlight voltage needed. See section 4.3.4 for further details.

# 3.7.12 J12: Flat Panel (Hirose connector)

Type: Hirose 31-pin connector, 1mm pitch, #DF9B-31P-1V

Recommended mating connector: Hirose DF9B-31S-1V

This connector houses the signals to drive an 18-bit flat panel and will drive a Sharp LQ64D343 panel in StrongARM  $^{TM}$  16-bit mode directly. It can be found on the back side of the Graphics Client Plus. The only difference between this connector and J14 is that J12 does not include  $V_{\rm EE}$ . Signals shown are for the StrongARM  $^{TM}$  in 16-bit mode. See section 3.7.14 for further details.

Electrical specifications for panel signals are listed in section 4.8.4.

| Pin | Signal name | Description                                               |  |

|-----|-------------|-----------------------------------------------------------|--|

| 1   | PNL_GND     | Panel ground                                              |  |

| 2   | PNL_PIXCLK  | Pixel Clock                                               |  |

| 3   | PNL_HSYNC   | Horizontal Sync.                                          |  |

| 4   | PNL_VSYNC   | Vertical Sync.                                            |  |

| 5   | PNL_GND     | Ground                                                    |  |

| 6   | PNL_RED0    | Red Bit 0 (same as RED5)                                  |  |

| 7   | PNL_RED1    | Red Bit 1                                                 |  |

| 8   | PNL_RED2    | Red Bit 2                                                 |  |

| 9   | PNL_RED3    | Red Bit 3                                                 |  |

| 10  | PNL_RED4    | Red Bit 4                                                 |  |

| 11  | PNL_RED5    | Red Bit 5                                                 |  |

| 12  | PNL_GND     | Ground                                                    |  |

| 13  | PNL_GREEN0  | Green Bit 0                                               |  |

| 14  | PNL_GREEN1  | Green Bit 1                                               |  |

| 15  | PNL_GREEN2  | Green Bit 2                                               |  |

| 16  | PNL_GREEN3  | Green Bit 3                                               |  |

| 17  | PNL_GREEN4  | Green Bit 4                                               |  |

| 18  | PNL_GREEN5  | Green Bit 5                                               |  |

| 19  | PNL_GND     | Ground                                                    |  |

| 20  | PNL_BLUE0   | Blue Bit 0 (same as BLUE5)                                |  |

| 21  | PNL_BLUE1   | Blue Bit 1                                                |  |

| 22  | PNL_BLUE2   | Blue Bit 2                                                |  |

| 23  | PNL_BLUE3   | Blue Bit 3                                                |  |

| 24  | PNL_BLUE4   | Blue Bit 4                                                |  |

| 25  | PNL_BLUE5   | Blue Bit 5                                                |  |

| 26  | PNL_GND     | Ground                                                    |  |

| 27  | PNL_LBIAS   | Enable                                                    |  |

| 28  | PNL_PWR     | Vcc(5V) or 3.3 V, depending on JP1 position               |  |

| 29  | I IVL_I VVI | vec <sub>(5 v)</sub> or 5.5 v, depending on 31 1 position |  |

| 30  | PNL_RL      | Horizontal Mode Select (set by JP2)                       |  |

| 31  | PNL_UD      | Vertical Mode Select (set by JP3)                         |  |

# 3.7.13 J13: Backlight Inverter

Type: 7-pin header, 1.25mm, keyed, Molex #53261-0790

Recommended mating connector: Molex 51021-0700 or

Quadrangle Products kit #RT51021-

0700-18

This connector will supply power to a Xentek LS520 backlight inverter and compatible devices with a one-to-one cable. The onboard Graphics Client Plus PWM driver can electronically control the brightness of the inverter.

| Pin | Signal name  | Description                                                                                  |

|-----|--------------|----------------------------------------------------------------------------------------------|

| 1   | +12V         | 0-12 volts from J5.4                                                                         |

| 2   | +12V         | (see J5 and section 4.3.4)                                                                   |

| 3   | GND          | Ground                                                                                       |

| 4   | GND          | Grouna                                                                                       |

| 5   | BACKLIGHTON  | Open-collector output with 12V pullup to control backlight (short to GND when LS520 is "on") |

| 6   | BACKLIGHTPWM | PWM brightness control (3.3V CMOS, 1.2k $\Omega$ series, 1uF filter)                         |

| 7   | GND          | Ground                                                                                       |

# 3.7.14 J14: Flat Panel (IDC 34)

Type: 34-pin IDC header, 2x17 0.100-inch spacing, shrouded, keyed

Recommended mating connector: IDC connector AMP #1-746288-8

The J14 connector houses the signals to drive an 18-bit flat panel. Electrical specifications for panel signals are listed in section 4.8.4. See notes following for details about creating cables.

| Pin | Signal name | Description                                                                  |

|-----|-------------|------------------------------------------------------------------------------|

| 1   | PNL_VEE     | $V_{EE}$ (contrast); see VR1, J19 and JP12                                   |

| 2   | PNL_GND     | Ground                                                                       |

| 3   | PNL_PIXCLK  | Pixel Clock                                                                  |

| 4   | PNL_HSYNC   | Horizontal Sync.                                                             |

| 5   | PNL_VSYNC   | Vertical Sync.                                                               |

| 6   | PNL_GND     | Ground                                                                       |

| 7   | PNL_RED0    | Red Bit 0 (same as RED5)                                                     |

| 8   | PNL_RED1    | Red Bit 1                                                                    |

| 9   | PNL_RED2    | Red Bit 2                                                                    |

| 10  | PNL_RED3    | Red Bit 3                                                                    |

| 11  | PNL_RED4    | Red Bit 4                                                                    |

| 12  | PNL_RED5    | Red Bit 5                                                                    |

| 13  | PNL_GND     | Ground                                                                       |

| 14  | PNL_GREEN0  | Green Bit 0                                                                  |

| 15  | PNL_GREEN1  | Green Bit 1                                                                  |

| 16  | PNL_GREEN2  | Green Bit 2                                                                  |

| 17  | PNL_GREEN3  | Green Bit 3                                                                  |

| 18  | PNL_GREEN4  | Green Bit 4                                                                  |

| 19  | PNL_GREEN5  | Green Bit 5                                                                  |

| 20  | PNL_GND     | Ground                                                                       |

| 21  | PNL_BLUE0   | Blue Bit 0 (same as BLUE5)                                                   |

| 22  | PNL_BLUE1   | Blue Bit 1                                                                   |

| 23  | PNL_BLUE2   | Blue Bit 2                                                                   |

| 24  | PNL_BLUE3   | Blue Bit 3                                                                   |

| 25  | PNL_BLUE4   | Blue Bit 4                                                                   |

| 26  | PNL_BLUE5   | Blue Bit 5                                                                   |

| 27  | PNL_GND     | Ground                                                                       |

| 28  | PNL_LBIAS   | Enable                                                                       |

| 29  | PNL_PWR     | Vcc(5V) or 3.3 V, depending on JP1 position                                  |

| 30  | TIVL_T WK   | vcc(5v) or 5.5 v, depending on 31 1 position                                 |

| 31  | PNL_RL      | Horizontal Mode Select (set by JP2)                                          |

| 32  | PNL_UD      | Vertical Mode Select (set by JP3)                                            |

| 33  | PNL_ENA     | Panel enable signal (StrongARM <sup>TM</sup> GPIO24)                         |

| 34  | VCON        | Adjustable voltage for passive panels; set with VR2 or fixed voltage divider |

The ADS signal names shown in the table above are for 16-bit color from the StrongARM<sup>TM</sup>. Where high-color is not required and the application works better with faster system performance, many developers choose to run their systems at 12-bit color. Standard ADS evaluation systems are built to deliver 12-bit color.

As part of its configuration service, ADS creates cable drawings and prototypes for many panels. ADS offers this service due to the complexity of interfacing to digital flat panel displays. However, if you wish to create your own cable to connect the Graphics Client Plus, there are a number of items to keep in mind:

- If you change the cable between 12- and 16-bit color without changing the display driver, the colors will be incorrect on the display. This will not damage the panel, but is inconvenient to work with.

- The StrongARM<sup>TM</sup> maps different signals to its pins based on the type of panel it is connected to. This allows unused pins to be utilized for other tasks, but can create confusion when you change panel display modes.

Consult the following table for signal mapping to the processor. Recall that the GC Plus signal names are for 16-bit color. For further information, please consult the StrongARM $^{TM}$  manual.

| J14 | Signal name |                         |  |

|-----|-------------|-------------------------|--|

| pin | GC Plus     | StrongARM <sup>TM</sup> |  |

| 22  | PNL_BLUE1   | LDD0                    |  |

| 23  | PNL_BLUE2   | LDD1                    |  |

| 24  | PNL_BLUE3   | LDD2                    |  |

| 25  | PNL_BLUE4   | LDD3                    |  |

| 26  | PNL_BLUE5   | LDD4                    |  |

| 21  | PNL_BLUE0   | LDD4                    |  |

| 14  | PNL_GREEN0  | LDD5                    |  |

| 15  | PNL_GREEN1  | LDD6                    |  |

| 16  | PNL_GREEN2  | LDD7                    |  |

| 17  | PNL_GREEN3  | LDD8                    |  |

| 18  | PNL_GREEN4  | LDD9                    |  |

| 19  | PNL_GREEN5  | LDD10                   |  |

| 8   | PNL_RED1    | LDD11                   |  |

| 9   | PNL_RED2    | LDD12                   |  |

| 10  | PNL_RED3    | LDD13                   |  |

| 11  | PNL_RED4    | LDD14                   |  |

| 12  | PNL_RED5    | LDD15                   |  |

| 7   | PNL_RED0    | LDD15                   |  |

| 3   | PNL_PIXCLK  | L-PCLK                  |  |

| 4   | PNL_HSYNC   | L-LCLK                  |  |

| 5   | VSYNC       | L-FCLK                  |  |

| 28  | PNL_LBIAS   | L-BIAS                  |  |

| 33  | PNL_ENA.H   | GPIO24                  |  |

# 3.7.15 J15: Manufacturing Test

Type: 2x3 header, 0.100-inch spacing

For manufacturing use.

## 3.7.16 J16: Speaker

Type: 2-pin header, 0.100-in spacing, friction lock, Molex 22-23-2021

Recommended mating connector: Molex 22-01-3027

A speaker may be connected across the speaker outputs (bridge-tied load). Minimum speaker impedance is eight ohms. Voltages on the speaker outputs are 0-3.3V. If you connect one side of the speaker to ground, you must use a blocking capacitor; in this case, output power will be reduced to one quarter and power consumption will be cut in half from that of the bridge-tied load. Consult the UCB1200 specifications for further details.

| Pin | Signal name | Description            |

|-----|-------------|------------------------|

| 1   | SPK -       | Speaker connection (-) |

| 2   | SPK +       | Speaker connection (+) |

# 3.7.17 J17: Microphone

Type: 2-pin header, 0.100-in spacing, friction lock, Molex 22-23-2021

Recommended mating connector: Molex 22-01-3027

Input impedance of the microphone connection is  $25 \text{ k}\Omega$ . Specifications for the UCB1200 call for  $1\text{k}\Omega$  or electret microphones. Microphones with other impedance may be used. Microphones connected should use a DC blocking capacitor between the microphone and MIC+ input.

| Pin | Signal name | Description    |  |

|-----|-------------|----------------|--|

| 1   | MIC GND     | Microphone (-) |  |

| 2   | MIC +       | Microphone (+) |  |

#### 3.7.18 J18: CAN Bus

Type: 2-pin header, 0.100-in spacing, friction lock, Molex 22-23-2021

Recommended mating connector: Molex 22-01-3027

Use this connection to connect to a CAN bus. Note that a CAN bus must be terminated at both ends with  $120\Omega$  resistors. The Graphics Client Plus does not include termination resistors onboard.

| Pin | Signal name | Description |

|-----|-------------|-------------|

| 1   | CAN1HIGH    | CAN bus (+) |

| 2   | CAN1LOW     | CAN bus (-) |

# 4 System Integration

## 4.1 Tips for System Integration

#### 4.1.1 Strategies for Backup Power

There are several ways to provide backup power to the Graphics Client Plus. Each has advantages that favor particular applications.

- **1. No Battery Backup.** Applications that are entirely non-volatile (no critical data is stored in RAM), or that can recover from unexpected power failures, are good candidates for doing without a backup battery.

- **2. 3V Battery on J3.** The backup battery supplies power to the system if the onboard 3.3V supply fails. Operating systems with power management will put the system to sleep if they detect that the system is operating from this supply. For this reason, the voltage on J3 must be consistently less than 3.3V (preferably less than 3.2 V).

- **3.** Use VPERM Input. The VPERM power source is more flexible than the backup battery in that it can be any voltage between 5 and 12 volts. Set JP5 to use this voltage for sleep mode power. Sleep mode power to the RAM is supplied through a linear regulator, so lower values of VPERM will provide lower sleep mode power consumption.

- **4.** Use Main Power as Backup. If the main power supply will be available continuously, set JP5 to use this voltage for sleep mode power. However, all 5V devices onboard (e.g. flash, PCMCIA) will continue to be under power during sleep mode, so power savings will be reduced.

#### 4.1.2 Electrical Tips

Keep the following issues in mind when designing a system using the Graphics Client Plus.

- Make sure that the 5V and 3.3V input voltage is stable, clean and robust (computer grade). Droops and instability in the 5V supply can result in erratic operation of PCMCIA cards and the flash memory.

- Route the touch panel cabling away from the backlight inverter and other noisy systems.

The touch panel driver algorithms can be adjusted to filter out large amounts of noise; however, the touch panel may then be less responsive.

- The backlight frequency can resonate with some flat panels. If beats appear, change the backlight frequency or panel refresh rate.

#### 4.2 **Mechanical Specifications**

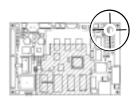

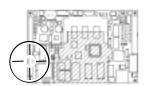

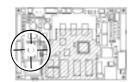

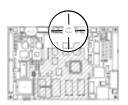

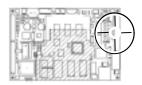

The diagram on the following page illustrates the dimensions of the Graphics Client Plus, as well as locations of key components on the board. Note that the origin for measurements is the center of the mounting hole on the lower left corner of the board.

# 4.2.1 Mechanical Drawing of Graphics Client Plus

Below is the mechanical drawing of the Graphics Client Plus. This image is also available in PDF format from ADS.

PCMCIA ejectors are available. These are the same height as the rest of the PCMCIA socket and extend beyond the forward edge of the board. The footprint is shown as crosshatching in the drawing.

#### 4.2.2 Mounting Holes

Four holes are provided, one on each corner, for mounting; the diameter of the holes is 0.138-in. Mounting holes are plated through and connected to the Graphics Client Plus ground plane.

For reliable ground connections, use locking washers (star or split) when securing a Graphics Client Plus in an enclosure. Make sure that washers do not extend beyond the limits of the pads provided.

#### 4.2.3 Clearances

The Graphics Client Plus has a low profile. It can fit in an enclosure as thin as 0.75-in I.D. Key clearances are as follows:

Highest component: 0.625 inches

• Minimum clearance under board: 0.2 inches

• Minimum overall height requirement: 0.75 inches

Note: Selection of connectors and wiring harnesses will determine height of final assembly.

# 4.3 Input Power Requirements

Power is supplied to the Graphics Client Plus through connect J5. A backup battery may also be connected to J3. All power inputs have EMI filtering. The following are the power inputs to the Graphics Client Plus.

#### 4.3.1 +5.0V

The Graphics Client Plus requires a high-quality DC input of 5.0 VDC ( $\pm 5\%$ ) to operate normally. This voltage is used to generate additional onboard voltages, but also supplies many ICs directly. For this reason, it should be well regulated and filtered. The 5V supply enters the board on pin 1 of J5.

The quality of the 5V supply is very important. Droop or instability in this supply can lead to intermittent failures of board systems including, but not limited to the PCMCIA slot and flash disk.

Note: Some configurations that do not have all options populated can tolerate voltages different from 5.0V on this input. Consult ADS if you think this will be necessary or useful for your application.

#### 4.3.2 +3.3V

You may want to supply 3.3V power to the Graphics Client Plus in the following cases:

- The 3.3V power supply option is not installed in your build of the Graphics Client Plus

- Additional 3.3V current is needed (e.g. for flat panel) than the Graphics Client Plus can supply

In either case, you must set JP6 to "External 3.3V" to utilize the external power. As with the 5V supply, the 3.3V power must be of the highest quality, as it supplies many ICs directly. An external 3.3V power is supplied to the Graphics Client Plus on pin 3 of J5.

#### 4.3.3 **VPERM**

If JP5 is set to use it, VPERM will supply power to the real-time clock and to DRAM during sleep mode. VPERM can be any voltage between 5 and 12 volts and is regulated down to 3.3V internally. VPERM enters the Graphics Client Plus on pin 6 of J5.

## 4.3.4 +12V

The "+12V" input supplies power to the backlight connector (J13) and  $V_{PP}$  on the PCMCIA sockets (J11). Because modern PCMCIA cards rarely use  $V_{PP}$ , this voltage can usually be set to any voltage between 0 and 12V to match the needs of the backlight inverter. If the backlight is not

connected to J13, this voltage can be left unconnected. "+12V" is supplied to the board on pin 4 of J5.

# 4.3.5 3.0V Battery Backup (J3)

Your system may include an external 3.0V battery to back up RAM and the real-time clock during sleep mode. If this voltage exceeds 3.1V it may interfere with power management circuits. See section 4.1.1 *Strategies for Backup Power* for details on power management.

# 4.3.6 "Power On" Output

Use the "Power On" output from J5 pin 5 to control external power supplies (e.g. 5V and 3.3V) if power conservation is important. This signal is high when the system is running and low when the system is asleep.

Note that the VPERM voltage, if used, should remain on regardless of the state of the Power On signal.

#### 4.3.7 EMI/RFI and Transient Suppression

It is the responsibility of the user to provide surge protection on the input power lines. This is especially important if the power supply wires will be subject to EMI/RFI or ESD.

# 4.4 Externally Available Voltages

The Graphics Client Plus generates voltages for the processor and other onboard logic. Some of these power sources are available externally as follows:

|                    | Maximum            |                     |

|--------------------|--------------------|---------------------|

| Voltage            | Output Current     | Connector           |

| VCC (+5V)          | $500 \text{ mA}^2$ | J7, pin 35          |

| +3.3V              | 100 mA             | J7, pin 37          |

| 5V, keyboard       | 350mA              | J6, pin 4           |

| Panel Power (based | 250 mA             | J12, pins 28 and 29 |

| on JP1 setting)    | 230 IIIA           | J14, pins 29 and 30 |

| Panel Vee          | 25 mA              | J14, pin 1          |

\_

<sup>&</sup>lt;sup>2</sup> Primarily dependent on external 5V power supply, but also limited by connectors and power plane on board.

## 4.5 **Power Consumption**

The Graphics Client Plus has been designed to use a minimum of power. When not active, the SA-1110 can be put into Idle or Sleep modes, further reducing power consumption.

The following measurements were made using production boards running Windows CE at 5.0 V. Power consumption ranges from 1W on a board with limited options<sup>3</sup> installed to about 3.5W for a fully-populated Graphics Client Plus running at full speed and driving a color TFT panel.

| Mode                       | Fully populated,<br>board only (mA) | Fully populated, driving<br>Sharp LQ64D343 panel<br>(mA) <sup>4</sup> |

|----------------------------|-------------------------------------|-----------------------------------------------------------------------|

| 206 MHz                    | 400                                 | 690                                                                   |

| Sleep (VPERM) <sup>5</sup> | 2.5                                 | 2.5                                                                   |

| Sleep (VBATT)              | 2.2                                 | 2.2                                                                   |

Note that actual power consumption will vary according to input voltage, temperature, panel selection and processor and peripheral activity.

## 4.6 **Power Management**

If Main Power fails, the Graphics Client Plus automatically switches to Backup Power. This source maintains the onboard RAM, the CPU real-time clock, and a few very lower power system circuits, but does not supply power to the processor.

The Graphics Client Plus generates an interrupt when the main power fails. It is the responsibility of the operating system or application to handle the power failure condition. In general, the operating system should shut down operations, prepare for a wakeup condition (external interrupt, system timer wakeup, etc), then put the system to sleep. Consult the reference manual for the operating system you are using.

Important: When in sleep mode, the system continues to draw 3.3 and 5V power. Use the Power\_On signal to turn off main power supplies during sleep (see J5 and section 4.3.6 for details).

#### 4.7 **EMI/RFI and ESD**

The Graphics Client Plus incorporates a number of industry-leading features that protect it from electrostatic discharge (ESD) and suppress electromagnetic and radio-frequency interference (EMI/RFI) . Transient voltage suppressors, EMI fences, filters on I/O lines and termination of high-frequency signals are included standard on all systems.

Many products using ADS single-board computers have successfully completed FCC emissions testing as a part of their design cycle. Because ADS supplies only the single-board computer and not fully integrated systems, ADS cannot provide meaningful system-level emissions test results.

<sup>&</sup>lt;sup>3</sup> Unit tested was a fully-populated, 32MB SA-1100 Graphics Client board with the Ethernet, V<sub>EE</sub> and ADSmartIO<sup>TM</sup> options not installed.

<sup>&</sup>lt;sup>4</sup> Refresh rate of panel in these tests was varied in direct proportion to CPU speed, i.e. pixel clock divider was constant across tests. The panel consumes more power at higher refresh rates.

<sup>&</sup>lt;sup>5</sup> Sleep mode test conditions: 1. Set Vperm=5V, 2. put system to sleep, 3. disconnect all other external power, 4. measure current (Iperm).

# 4.8 Electrical Specifications for I/O Ports

# 4.8.1 ADSmartIO<sup>TM</sup> Controller

As Digital Outputs:

Push-pull 3.3V CMOS Sink up to 20 mA

As Digital Inputs:

CMOS,  $V_{DD}$ =3.3V (3.8V max) Logical low @ <0.3  $V_{DD}$ , logical high @ > 0.6 $V_{DD}$ Software-selectable MOS pull-ups, 35-120k $\Omega$

As Analog Inputs (Port A/Columns):

10-bit, 0 -  $V_{ref}$  (~2.4V)

Input impedance:  $100M\Omega$ , with overvoltage protection

$V_{max} = V_{DD} = 3.3V$

Additional information:

Row and column I/Os have  $1k\Omega$  series resistance and overvoltage protection to ground. SMTIO0-5 I/Os are directly connected to I/O controller without external protection. Control pullup resistors by writing to bits of IO port when the port is configured as a digital input (bit mask 1=enable, 0=disable).

#### 4.8.2 UCB 1200

As Digital Outputs:

Push-pull 3.3V CMOS

Maximum output current: 4 mA

As Digital Inputs:

CMOS,  $V_{DDD}$ =3.3V (3.8V max) Logical low @ <0.3  $V_{DDD}$ , logical high @ > 0.7 $V_{DDD}$

Analog Inputs:

10-bit, 0~9.9V (11.0V max)

Input impedance:  $1.3k\Omega$  (0.76 voltage divider) Range of maximum reading (0x3ff): 9.2-10.5V.

Additional information:

Digital I/Os have  $1k\Omega$  series resistance with overvoltage protection.

#### 4.8.3 SA-1110

As Digital Outputs:

Push-pull 3.3V CMOS

Maximum output current: 2 mA

As Digital Inputs:

CMOS,  $V_{DDX}$ =3.3V (3.6V max) Logical low @ <0.2  $V_{DDX}$ , logical high @ > 0.8 $V_{DDX}$

Additional information:

Digital I/Os GPIO24-27 have  $1k\Omega$  series resistance GPIO24 also has  $10k\Omega$  pull-down and controls the buffered PNL\_ENA signal (3.7.14).

#### 4.8.4 LCD Panel

LCD display panels have a wide range of voltage and data requirements. The Graphics Client Plus has a number of adjustable voltages to support these requirements.

PNL\_PWR:

Voltage is 3.3 or 5V, depending on setting of JP1. Must be set to match panel specifications.

Vee:

Bias voltage used for many passive panels.

Can be positive, negative or fixed at "12V" (from J5). Selected with J19.

Adjustable with VR1; typically in the range of 20 to 30V.

Voltage and current range can be changed at the factory for specific panels or needs.

VCON:

Voltage used by some panels to adjust contrast.

Adjustable between 0V and PNL\_PWR with  $10k\Omega$  potentiometer VR2.

VCON is populated as needed, and may not be available on some evaluation systems.

In production, VCON can be set to a specific value with fixed resistors.

(This page intentionally blank)

# 5 Board Revision History

#### 5.1.1 Identifying the board revision

The product revision number of the Graphics Client Plus is etched on the underside of the printed circuit board. That number is 170110-8000x, where "x" is the board revision.

## 5.1.2 Revision History

The Graphics Client Plus was based on the successful design of its SA-1100 predecessor, the Graphics Client. For that reason, few changes have been made to its design since its introduction.

The following are the most significant changes that have occurred.

#### Rev. A:

• (See section 1.2 for differences from Graphics Client)

#### Rev. B:

- Corrects reversal of Serial 2 RX/TX (no jumper wires required on JP7)

- Supports 3.3 and 5V RS-485 drivers

(This page intentionally blank)