# **USER MANUAL**

# Catalyst EC Embedded Computer System

Rev. A - July 2010 - 110123-4000A

#### **Disclaimer**

The information in this document is subject to change without notice and should not be construed as a commitment by any Eurotech company. While reasonable precautions have been taken, Eurotech assumes no responsibility for any error that may appear in this document.

#### **Trademarks**

All product or service names are the property of their respective owners.

#### **Document Revision History**

| Issue no. PW | 'B Date   | Comments                                                                                                                                                                                                                               |

|--------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3            | Nov-2008  | Initial release                                                                                                                                                                                                                        |

| 4            | Aug-2009  | Updates for revision A carrier board, touch screen, power indictors, and development kits Appendix E added                                                                                                                             |

| Ā            | July-2010 | Updates for Catalyst Module XL, backlight signal type, EIA-232 mode on J17 and J18, mounting hole connectivity, and input power specification ESF information added Recommendations for hard drive cable length and PWB mounting added |

© 2008 Eurotech Inc.

For contact details, see page 61.

# **Contents**

| Introduction                                  |    |

|-----------------------------------------------|----|

| Block Diagram                                 | 6  |

| Features                                      | 7  |

| Related Documents                             | 9  |

| Handling Your Board Safely                    | 9  |

| Conventions                                   | 10 |

| Software Specification                        | 11 |

| Operating System Support                      |    |

| Drivers                                       |    |

| BIOS                                          |    |

| Everyware <sup>™</sup> Software Framework     |    |

| Hardware Specification                        |    |

| Core Processor                                |    |

| Memory                                        |    |

| Synchronous DRAM                              |    |

| Non-volatile Memory                           |    |

| BIOS and Configuration Data                   |    |

| Real-Time Clock                               |    |

| External Memory Interfaces                    |    |

| PATA Drive                                    |    |

| SD/MMC Card                                   |    |

| USB Disk Drive                                |    |

| Embedded USB Mass Storage Drive (optional)    |    |

| Communications                                |    |

| Universal Serial Bus                          |    |

| Serial Ports                                  |    |

| Wireless Module or Mini PCI Express Interface |    |

| Ethernet                                      |    |

| I <sup>2</sup> C Bus                          |    |

| System Management Bus                         |    |

| User Interface and Display                    |    |

| LVDS Display                                  |    |

| Analog RGB                                    |    |

| Touch Panel                                   |    |

| Backlight                                     |    |

| PS/2 Keyboard and Mouse                       |    |

| Discrete I/O                                  |    |

| I/O Expansion Port                            |    |

| Super I/O Controller                          |    |

| System Monitoring                             |    |

| Temperature                                   |    |

| Voltage                                       |    |

| Tachometer                                    |    |

| Audio Interface                               | 23 |

| Power and Power Management                      | 23 |

|-------------------------------------------------|----|

| Power Supply Architecture                       | 24 |

| ACPI Power Management States                    | 24 |

| Mechanical                                      | 26 |

| Connectors, Switches, Jumpers, and Indicators   | 28 |

| Identifying Connectors                          | 28 |

| Switches, Jumpers, and Indicators               | 28 |

| SW1: Reset                                      | 28 |

| SW2: On/Off                                     | 28 |

| J35: USB Host/Client Jumper                     | 29 |

| J36: PCIe Multiplexer Jumper                    | 29 |

| Carrier Board LED Indicators                    | 29 |

| Ethernet LEDs                                   |    |

| Signal Headers                                  | 31 |

| J1: Docking Connector: Data                     |    |

| J2: Docking Connector: Power                    |    |

| J3: JTAG                                        |    |

| J4: Maintenance Port                            |    |

| J5: Power Input                                 |    |

| J6: GPIO                                        |    |

| J7: Ethernet 0 and Ethernet 1                   |    |

| J8: USB Host 0                                  |    |

| J9: USB Host 1                                  |    |

| J10: USB Host 2 or USB Client                   |    |

| J11: USB Host 3                                 |    |

| J12: Stereo Line Out 0 and Stereo Line In 0     |    |

| J13: Stereo Line Out 1 and Stereo Line In 1     |    |

| J14: Analog RGB                                 |    |

| J15: Serial 1                                   |    |

| J16: Serial 2                                   |    |

| J17: Serial 3                                   |    |

| J18: Serial 4                                   |    |

| J19: Serial 5 and Wireless Module Power Control |    |

| J20: PS/2 Keyboard                              |    |

| J21: PS/2 Mouse                                 |    |

| J22: LVDS Display, Backlight, and Touch Panel   |    |

| J23: SD/MMC                                     | _  |

| J24: PATA Interface                             |    |

| J25: Touch Panel, Wake, and GPIO                |    |

| J26: Wireless Module or Mini PCle Interface     |    |

| J32: I <sup>2</sup> C Bus                       |    |

| J33: SMBus                                      |    |

| J34: Embedded USB Mass Storage Drive (optional) |    |

| System Specification                            |    |

| Performance                                     |    |

| Power Supply                                    | 48 |

| Electrical                         | 49 |

|------------------------------------|----|

| Universal Serial Bus               | 49 |

| I <sup>2</sup> C Bus               | 49 |

| SMBus                              | 49 |

| Analog RGB                         | 50 |

| LVDS Display                       |    |

| Touch Panel Controller             | 50 |

| Backlight                          | 51 |

| General-Purpose Inputs and Outputs | 51 |

| Super I/O Controller               | 52 |

| Audio Interface                    | 52 |

| General                            | 53 |

| Crystal Frequencies                | 53 |

| Real-Time Clock                    | 53 |

| Environmental                      | 53 |

| Appendix A – Reference Information | 54 |

| Appendix B – RoHS Compliance       | 56 |

| Appendix C – Board Revision        | 57 |

| Appendix D – Development Kit       |    |

| Appendix E – Maintenance Port      |    |

# Introduction

The Catalyst Module XL is a high-performance, low-power module based on the Intel<sup>®</sup> Atom<sup>™</sup> processor. It uses an integrated two-chip solution comprised of the Intel Atom processor and Intel<sup>®</sup> System Controller Hub US15W (Intel<sup>®</sup> SCH US15W). The Intel Atom processor utilizes the new low-power Intel micro architecture, while the Intel SCH US15W contains an integrated 2D/3D graphics controller supporting hardware-accelerated graphics display and video processing capabilities. The Catalyst Module XL allows embedded users to gain higher performance with greater energy efficiency.

An EPIC form factor carrier board integrates with the Catalyst Module XL for a total production solution. The Catalyst EC carrier board implements industry-standard interfaces supporting a broad spectrum of end-use applications.

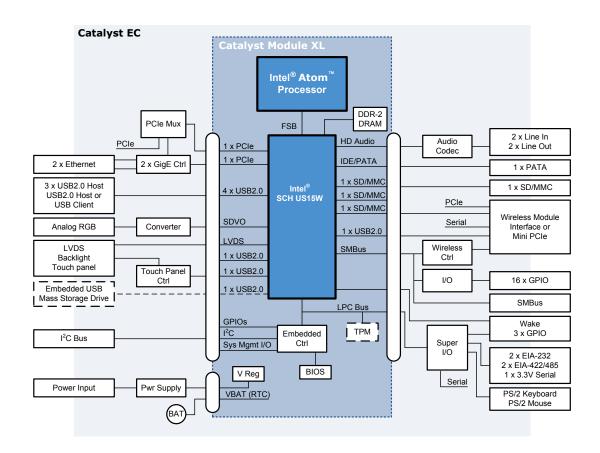

# **Block Diagram**

The following diagram illustrates the system organization of the Catalyst EC. Notice that the data connector on the Catalyst Module XL has been divided into two sections for this illustration. Options are shown with dotted lines.

#### **Features**

#### **Processor**

- Intel<sup>®</sup> Atom<sup>™</sup> processor

- Intel System Controller Hub US15W

- Clock rates of 1.1 GHz, 1.33 GHz, or 1.6 GHz

- Front side bus from 400 MHz to 533 MHz

#### **Memory**

- 512 MB, 1 GB, or 2 GB DDR-2 DRAM

- System BIOS flash memory

- Battery-backed real-time clock

- External memory support

- PATA disk drive

- USB disk drive

- SD/MMC card

- Embedded USB Mass Storage drive (optional)

#### **Communications**

- Five USB 2.0 ports

- Three host ports operating at low, full, and high speeds

- USB host port or USB client port (alternate configuration)

- One host port for wireless module support

- Six serial ports

- Two EIA-232, 9-wire

- Two EIA-422/485 or EIA-232, 4-wire

- One LVTTL, 3-wire

- One LVTTL for wireless module support

- · Wireless module or Mini PCIe socket

- Wireless module support for 802.11 b/g WLAN, Bluetooth, and GPS

- Mini PCIe socket (alternate configuration)

- Up to two 10/100/1000 Mbps Ethernet ports

- System Management Bus (SMBus)

- I<sup>2</sup>C bus with I<sup>2</sup>C master device

#### **Audio Interface**

- Two stereo line inputs

- Two stereo line outputs

- PC beep support

#### **User Interface and Display**

- Two independent display outputs

- LVDS

- Analog RGB

- Resistive touch panel (4-, 5-, or 8-wire options)

- Backlight interface with control signals for intensity and on/off

- PS/2 keyboard and mouse support

#### **Inputs and Outputs**

- Nineteen general-purpose inputs and outputs

- Wake input

#### **Power Supply**

- 8-16 V main power input

- Optional custom input protection for a 6-28 V main power input

- ACPI power management

#### Mechanical

• EPIC form factor (165 mm x 115 mm)

#### **Environmental**

- Extended-operating temperature

- FCC Class A compliant

- RoHS compliant

- IPC-A-610 compliant assembly process

110123-4000A

## **Related Documents**

This document describes the Catalyst EC and is intended for software application developers and system integrators. A system-level overview of the Catalyst EC is provided in the following sections. The following documents are also important resources for developing applications for the Catalyst EC.

| Document                                         |             |

|--------------------------------------------------|-------------|

| Catalyst Module Design-In Guide                  | 110122-2003 |

| Catalyst EC Development Kit with LCD Quick Start | 110123-4001 |

| Catalyst EC Development Kit Quick Start          | 110123-4002 |

Check the Eurotech support site (<a href="http://support.eurotech-inc.com/">http://support.eurotech-inc.com/</a>) for errata reports and for the latest releases of these documents.

# **Handling Your Board Safely**

#### **Anti-Static Handling**

The Catalyst EC contains CMOS devices that could be damaged by electrostatic discharge (ESD). Observe industry-standard electronic handling procedures when handling the board. Where possible, work on a grounded anti-static mat. At a minimum, touch an electrically grounded object before handling the board or touching any components on the board.

#### **Packaging**

Please ensure that, should a board need to be returned to Eurotech, it is adequately packed, preferably in the original packing material.

#### **Electromagnetic Compatibility**

The Catalyst EC is classified as a component with regard to the European Community Electromagnetic Compatibility (EMC) regulations. As a part of its design cycle, the Catalyst EC has successfully completed FCC and CE emissions testing and meets the FCC Class A requirements.

Because Eurotech supplies only the embedded computer system and not fully integrated systems, Eurotech cannot provide meaningful system-level emissions test results. It is the responsibility of the user to ensure that systems using the Catalyst EC are compliant with the appropriate EMC standards.

#### **RoHS Compliance**

The European RoHS Directive (Restriction on the use of certain Hazardous Substances – Directive 2002/95/EC) limits the amount of six specific substances within the composition of the product. The Catalyst EC fully complies with the RoHS directive. A full *RoHS Compliance Materials Declaration Form* for the Catalyst EC is included as Appendix B – RoHS Compliance, page 56. Further information regarding RoHS compliance is available on the Eurotech web site at <a href="https://www.eurotech.com">www.eurotech.com</a>. Additionally, the Catalyst EC is assembled in a lead-free process that also meets IPC-A-610 guidelines.

# **Conventions**

The following table lists the symbols used in this document.

| Symbol | Explanation                                                                                      |

|--------|--------------------------------------------------------------------------------------------------|

| i      | Note – information that requires your attention                                                  |

|        | Warning – proceeding with a course of action may damage your equipment or result in loss of data |

The following table describes the conventions for signal names used in this document.

| Convention | Explanation                          |

|------------|--------------------------------------|

| GND        | Digital ground plane                 |

| #          | Active low signal                    |

| +          | Positive signal in differential pair |

| -          | Negative signal in differential pair |

The following table describes the abbreviations for direction and electrical characteristics of a signal used in this document.

| Туре     | Explanation                         |

|----------|-------------------------------------|

| 1        | Signal is an input to the system    |

| 0        | Signal is an output from the system |

| Ю        | Signal may be input or output       |

| Р        | Power and ground                    |

| Α        | Analog signal                       |

| OD       | Open-drain                          |

| CMOS     | 3.3 V CMOS                          |

| LVTTL    | Low Voltage TTL                     |

| 5        | 5 V signal level                    |

| LVDS     | Low Voltage Differential Signalling |

| nc       | No connection                       |

| reserved | Use is reserved to Eurotech         |

110123-4000A

# **Software Specification**

Eurotech provides an application-ready platform including BIOS, operating system, and development environment. This section gives a brief description of the software support available for the Catalyst EC. For additional details, contact your local Eurotech technical support.

# **Operating System Support**

The Catalyst EC is compatible with the following operating systems:

- Windows<sup>®</sup> XP Professional

- Windows XP Embedded

- Windows Embedded Standard

- Windows CE 6.0

- Wind River Linux 3.0

- Select real-time operating systems

#### **Drivers**

System components have drivers available for the Windows operating system and Linux.

#### **BIOS**

The Catalyst EC incorporates a custom system BIOS developed by Eurotech.

#### PC Beep

The Catalyst EC supports PC beep providing optional beep codes for system activity, analysis, and error code indications.

# **Everyware** <sup>™</sup> Software Framework

Everyware Software Framework (ESF) is an inclusive software framework that puts a middleware layer between the operating system and the OEM application. It provides industry-standard interfaces that shorten development time, simplify coding, and allow software to be ported from one Eurotech hardware platform to another. ESF is available on the Catalyst EC.

Information about ESF is available at http://esf.eurotech.com.

# **Hardware Specification**

#### **Core Processor**

The Catalyst EC bases its architecture on the high-performance, low-power Catalyst Module XL. This module uses an integrated two-chip solution comprised of the Intel Atom processor and Intel SCH US15W. The module is available in various versions based on the following features:

- Processor speed

- On-module DRAM

- Operating temperature

For the various performance variants, see Performance, page 48.

# **Memory**

The Catalyst Module XL combined with a carrier board provides a variety of storage capabilities. The following sections describe the different types of memory supported by the Catalyst EC.

#### Synchronous DRAM

Double Data Rate Synchronous DRAM (DDR-2) is used on the Catalyst Module XL for system main memory and frame buffer memory. Modules are available with 512 MB, 1 GB, or 2 GB memory. The data bus supports 64-bit accesses with a maximum burst bandwidth of 4.2 GBps (8 B @ 533 MHz). The memory bus operates at the same frequency as the front side bus.

The Intel Atom processor supports unified memory architecture in which the integrated 2D/3D graphics controller memory is "unified" with the system main memory. The default frame buffer is 4 MB with an 8 MB option. BIOS Setup settings select the frame buffer size. Extended graphics memory space is available up to 256 MB. The graphics driver controls this size based on usage.

#### **Non-volatile Memory**

The Catalyst Module XL includes non-volatile memory for system BIOS storage and a real-time clock (RTC) functionality.

#### BIOS and Configuration Data

A serial interface flash memory device stores the BIOS boot firmware, BIOS Setup settings, and module configuration data on the Catalyst Module XL. Standard configuration is 1 MB. The flash device performs logically as a firmware hub (FWH) and connects to the on-module embedded controller using a serial peripheral interface (SPI). This system BIOS memory supports pre-programmability at the device level, in-circuit programming on module, and updates using a run-time flash utility. In addition, programmable write protection is available using multiple flash sectors.

110123-4000A

#### Real-Time Clock

The Catalyst Module XL includes a RTC function. It retains the system date and time when the system is powered down as long as the 3.3 V "always" power or backup power is provided to the module. To supply backup power, the Catalyst EC includes a long-life battery. For general specifications, see Real-Time Clock, page 53.

#### **External Memory Interfaces**

Four types of external memory interfaces provide mass storage options for the Catalyst EC. The carrier board includes a PATA header, a SD/MMC socket, four USB host ports, and an optional embedded USB mass storage drive interface that can connect external memory to the system.

#### PATA Drive

Parallel ATA (PATA) disk drives provide removable storage in a wide variety of capacities. The Catalyst EC supports an optional 2.5-inch PATA magnetic or solid-state disk drive on header J24, page 43. This capability can be a cost-effective means to expand system storage.

The Catalyst EC uses the ATA-50 cable pinout, which is commonly used for connecting 2.5-inch hard drives to laptop motherboards. Cable lengths should be kept short, especially if you want to reliably achieve the higher data rates of UDMA 4 or UDMA 5. Eurotech recommends that cables be less than six inches in length for high-speed use (UDMA4/5). For low-speed use, in no case should the cable be longer than ten inches.

#### SD/MMC Card

The Secure Digital and MultiMediaCard (SD/MMC) socket on the Catalyst EC enables mass storage and I/O expansion. Socket J23, page 43 connects to the Catalyst Module XL SD/MMC 0 interface. This interface provides 4-bit operation and supports the following specifications:

- MMC 4.0 specification allowing clock frequencies up to 48 MHz and bus widths of 1 or 4 bits

- SDIO 1.1 specification allowing clock frequencies up to 24 MHz and bus widths of 1 or 4 bits

#### USB Disk Drive

A USB disk drive can connect to one of four USB host ports on the carrier board: J8, J9, J10 and J11. For a description of these ports, see Universal Serial Bus, page 14.

#### Embedded USB Mass Storage Drive (optional)

Embedded USB mass storage drives provide high capacity in a small form factor. As a volume production option, the Catalyst EC includes header J34, page 47 to support this type of external memory. Examples of supported devices include the Micron RealSSD Embedded USB Mass Storage devices: MTFDCAE001SAF, MTFDCAE002SAF, MTFDCAE004SAF, and MTFDCAE008SAF.

#### **Communications**

The Catalyst EC supports several industry-standard channels for communication with peripheral and peer devices. These interfaces include USB, serial, wireless, PCIe x 1, Ethernet, I<sup>2</sup>C, and SMBus. The following sections describe these interfaces.

#### **Universal Serial Bus**

The Catalyst EC includes four general-purpose Universal Serial Bus (USB) ports. Three ports are dedicated USB host ports, while the fourth port supports USB host or USB client capability. All ports support the USB 2.0 specification.

The following table describes the four USB ports.

| Socket                   |                          | Speed                                  |

|--------------------------|--------------------------|----------------------------------------|

| Default                  | Alternate                |                                        |

| J8: USB Host 0, page 34  |                          |                                        |

| J9: USB Host 1, page 34  |                          | High (480 Mbps),<br>Full (12 Mbps), or |

| J10: USB Host 2, page 35 | J10: USB Client, page 35 | Low (1.5 Mbps)                         |

| J11: USB Host 3, page 35 |                          | , ,                                    |

#### USB Host Ports (default configuration)

In the default configuration, the Catalyst EC provides four USB host ports managed by the Catalyst Module XL. Connect client devices such as USB mouse, keyboard, and storage to these ports.

Support circuitry including power switch, current limiter circuit, common mode chokes, and over-current protection is included on the carrier board. The USB protocol allows client devices to negotiate the power they need from 100 mA to 500 mA in 100 mA increments. The Catalyst EC supplies 5 V power to each USB host port through a power switch with over-current detection. Make sure to account for power used through USB in your power budget. For electrical specifications, see Universal Serial Bus, page 49.

#### USB Client Port (alternate configuration)

Socket J10 can function as a USB host or USB client port. Jumper J35, page 29 selects the configuration of this port. By default, this jumper is not installed and socket J10 operates as a USB host port.

#### **Serial Ports**

The carrier board includes a Super I/O Controller that is connected to the Catalyst Module XL using the LPC Bus. This device provides six serial ports. Five serial ports are available for general-purpose serial communication. A sixth serial port is dedicated to the wireless module interface. For details about this port, see Wireless Module, page 15.

| The following | table de | secribae t  | ha fiva  | general r | nurnoca | carial | intarfaces  |

|---------------|----------|-------------|----------|-----------|---------|--------|-------------|

| THE IONOWING  | table ut | osciliacs t | IIC IIVC | general-p | Julpuse | SCHAI  | interiaces. |

| Header                 | Communications                              | Baud Rate                                      |

|------------------------|---------------------------------------------|------------------------------------------------|

| J15: Serial 1, page 38 | EIA-232, 9-wire                             | 50 bps to 230,400 bps                          |

| J16: Serial 2, page 38 | EIA-232, 9-wire                             | 50 bps to 230,400 bps                          |

| J17: Serial 3, page 39 | EIA-422/485 (default)<br>or EIA-232, 4-wire | 50 bps to 460,800 bps<br>50 bps to 115,200 bps |

| J18: Serial 4, page 39 | EIA-422/485 (default)<br>or EIA-232, 4-wire | 50 bps to 460,800 bps<br>50 bps to 115,200 bps |

| J19: Serial 5, page 40 | LVTTL, 3-wire                               | 50 bps to 1.5 Mbps                             |

For electrical specifications of Serial 5, see Super I/O Controller, page 52.

#### Wireless Module or Mini PCI Express Interface

The Catalyst EC supports either an Intel McCaslin platform compliant wireless module or a Mini PCI Express (Mini PCIe) card on socket J26, page 46. Jumper J36, page 29 selects the configuration of this socket. By default, this socket does not include a PCIe bus connection and conforms to the Intel McCaslin platform I/O pin definition.

Wireless Module (default configuration)

In the default configuration, the Catalyst EC supports an Intel McCaslin platform compliant module providing fully integrated 802.11 b/g WLAN, Bluetooth, and GPS solutions. This wireless module interface includes a 4-bit SD/MMC interface, a USB host port, a NEMA style GPS serial interface, three LED control signals, and five wireless control signals on socket J26, page 46.

A power switch included on the Catalyst EC enables sequencing of the power to socket J26. Header J19, page 40 includes a 2-pin jumper to control this power switch. By default, this jumper is not installed. With this jumper installed, socket J26 directly supports the Wi2Wi W2CBWG01 wireless module.

Application software controls the five wireless control signals using an I/O expansion device connected to the Catalyst Module XL SMBus. This device includes four registers: input port, output port, polarity inversion, and configuration. For details about accessing these registers, see System Management Bus, page 17.

Each wireless control signal is mapped to a bit in the output port register as defined in the following table.

| Bit | Function    | Description                              |

|-----|-------------|------------------------------------------|

| 7   | WIFI_PD#    | Wi-Fi power (0 = off, 1 = on)            |

| 6   | BT_RESET#   | Bluetooth power (0 = off, 1 = on)        |

| 5   | BT_WAKE     | Bluetooth wakeup (0 = sleep, 1 = wake)   |

| 4   | WIFI_RESET# | Wi-Fi reset (0 = reset, 1 = run)         |

| 3   | GPS_ON_OFF  | Pulsing this bit changes the power state |

| 2   | nc          |                                          |

| 1   | nc          |                                          |

| 0   | nc          |                                          |

Mini PCI Express (alternate configuration)

A key capability of the Catalyst Module XL is its PCle Express (PCle) support. The module provides two PCle x1 busses to the carrier board. Each bus supports 2.5 Gbps bandwidth in each direction.

One PCIe x 1 bus connects directly to Ethernet Controller 0, while the second bus connects to a PCIe port multiplexer on the carrier board. This multiplexer routes the second PCIe bus to either Ethernet controller 1 or to socket J26. Jumper J36, page 29 controls the PCIe multiplexer. By default, the PCIe bus is disconnected on socket J26. For additional information about the Ethernet interfaces, see Ethernet, page 16.

Note: Ethernet 1 is mutually exclusive with the PCIe bus connection on socket J26. The default configuration of jumper J36 selects Ethernet 1.

#### **Ethernet**

The Catalyst EC supports up to two 10/100/1000 Mbps Ethernet ports with individual MAC addresses. Contact your local Eurotech technical support about special programming of MAC addresses. The two Ethernet ports are included on socket J7, page 33. This dual RJ-45 socket also includes two Ethernet LEDs, page 30 and built-in magnetics for each Ethernet connection.

The carrier board includes two Intel 82574L Gigabit Ethernet Controllers. Ethernet Controller 0 connects directly to the Catalyst Module XL using a PCIe bus, while Ethernet Controller 1 connects to the Catalyst Module XL through a PCIe port multiplexer. Jumper J36, page 29 controls this multiplexer. By default, the Ethernet 1 interface is enabled.

#### I<sup>2</sup>C Bus

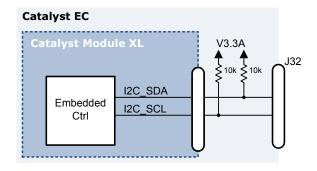

I<sup>2</sup>C (Inter-IC) is a multi-master, "two-wire" synchronous serial bus for communications between integrated circuits (ICs) and for addressing peripherals in a system. The Catalyst EC includes an external connection to the I<sup>2</sup>C bus of the Catalyst Module XL embedded controller on header J32, page 46. For electrical specifications, see I<sup>2</sup>C Bus, page 49.

The following diagram illustrates the I<sup>2</sup>C architecture on the Catalyst EC.

#### **System Management Bus**

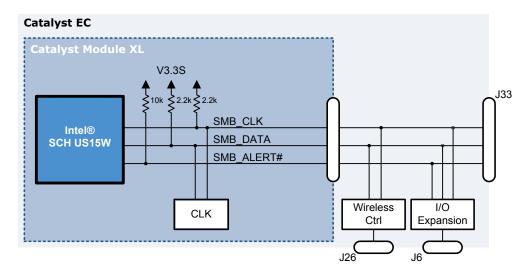

System Management Bus (SMBus) is a serial interface allowing multiple devices to communicate with each other. The Catalyst Module XL acts as bus master and uses this interface to communicate with devices on the carrier board or external to the carrier board on header J33, page 47. For electrical specifications, see SMBus, page 49.

The following diagram illustrates the SMBus architecture on the Catalyst EC. Notice that the I/O expansion port is connected to SMB\_ALERT#. The GPIOs on header J6 can generate system interrupts using this signal. This capability requires software support.

The following table lists the addresses of the SMBus devices on the Catalyst EC.

| Device             | Address   | Function |  |

|--------------------|-----------|----------|--|

| Catalyst Module XL |           |          |  |

| Reserved           | 0101 0010 | Write    |  |

|                    | 0101 0011 | Read     |  |

| Clock Generator    | 1101 0010 | Write    |  |

|                    | 1101 0011 | Read     |  |

| Carrier Board      |           |          |  |

| I/O Expansion      | 0100 0000 | Write    |  |

| GPIO 7:0           | 0100 0001 | Read     |  |

| I/O Expansion      | 0100 0010 | Write    |  |

| GPIO 15:8          | 0100 0011 | Read     |  |

| Wireless Control   | 0100 0100 | Write    |  |

|                    | 0100 0101 | Read     |  |

The following table lists the commands available for the SMBus devices on the carrier board.

| Carrier Board Device       | Command | Register                       |

|----------------------------|---------|--------------------------------|

| Wireless Control           | 0       | Input                          |

|                            | 1       | Output                         |

|                            | 2       | Reserved                       |

|                            | 3       | Reserved                       |

| I/O Expansion<br>GPIO 7:0  | 0       | Input                          |

|                            | 1       | Output                         |

|                            | 2       | Polarity<br>0=normal, 1=invert |

|                            | 3       | Direction<br>0=output, 1=input |

| I/O Expansion<br>GPIO 15:8 | 0       | Input                          |

|                            | 1       | Output                         |

|                            | 2       | Polarity<br>0=normal, 1=invert |

|                            | 3       | Direction<br>0=output, 1=input |

# **User Interface and Display**

The Catalyst EC provides two independent display interfaces. A 4-channel LVDS interface drives the primary display, while an analog RGB interface drives a secondary display. In addition, the Catalyst EC provides discrete backlight control signals and supports a 4-, 5-, or 8-wire resistive touch panel.

This section summarizes the Catalyst EC graphics display and video processing capabilities. Display resolutions are specified at the maximum refresh rate and color depth. Higher resolutions may be possible at lower refresh rates and color depths. This relationship is due primarily to the increased processing bandwidth required at higher output resolutions.

#### LVDS Display

The growing demand for higher resolution displays has been meet with design limitations on the interface between the LCD and graphics controller. Increased resolution LCDs require an increased clock speed, a larger number of data lines, and a higher power consumption. LVDS serial data transmission addresses these issues by providing a high-speed, low-power interface on a single pair of wires per channel.

The Catalyst EC provides an LVDS display output to drive a primary display on header J22, page 41. This interface consists of four LVDS data pairs, as well as an LVDS pixel clock, and supports 18-bit (6-bit RGB) or 24-bit (8-bit RGB) color. The carrier board includes an LVDS buffer/repeater with configurable pre-emphasis to drive lossy backplanes and cables. A standard Catalyst EC is configured for pre-emphasis off. Other configurations are available as volume production options.

The following table summarizes the LVDS display capabilities.

| Feature           | LVDS Display                                                                                                       |

|-------------------|--------------------------------------------------------------------------------------------------------------------|

| Resolution        | Single display up to 1366 x 768 at 85 Hz, 8-bit per lane or dual display up to 1280 x 768 at 85 Hz, 8-bit per lane |

| Configurations    | Extended Display Identification Data (EDID) and non-EDID                                                           |

| Operation         | Extended desktop or clone mode                                                                                     |

| Display parameter | Centering, scaling, and rotation                                                                                   |

Additional capabilities of the LVDS display output include software-controlled display power, display scan control, and an  $I^2C$  bus for communication with the display. The signals L\_CLK and L\_DATA are connected to the Catalyst Module XL LCD Display Data Channel (DDC)  $I^2C$  bus on a standard Catalyst EC. An alternate connection to the backlight  $I^2C$  bus is available as a volume production option. For electrical and power specifications, see LVDS Display, page 50.

#### **Analog RGB**

In addition to the LVDS display output, the Catalyst EC drives a secondary display on its analog RGB output. A Chrontel CH7317A Display Converter accepts the SDVO output from the Catalyst Module XL, encodes the data, and drives the analog RGB output. Signals from three 10-bit DACs internal to the display converter are mapped onto eightbit color channels for red, green, and blue data. Connector J14, page 37 provides the analog RGB output. For electrical specifications, see Analog RGB, page 50.

In addition to the 8:8:8 RGB data, the display controller provides a DDC bus on connector J14 for monitor Plug and Play.

#### **Touch Panel**

A USB controller and separate analog multiplexer included on the carrier board drives resistive touch panels. Header J22, page 41 includes the touch panel signals, while header J25, page 45 includes a 2-pin jumper to configure the touch panel. By default, the Catalyst EC supports 4-, 5-, and 8-wire touch panels. This section provides the signal mapping for these configurations. For electrical specifications, see Touch Panel Controller, page 50.

#### 4-Wire Touch Panel

The following table describes the wiring for 4-wire resistive touch panels on header J22.

| J22 Pin | Name      | 4-Wire | 4-Wire (Alternate) |

|---------|-----------|--------|--------------------|

| 26      | SX-       |        |                    |

| 28      | SY-       |        |                    |

| 30      | SY+       |        |                    |

| 32      | SX+ (TC3) | Right  |                    |

| 34      | TC4       | Bottom | Bottom             |

| 36      | TC2       | Тор    | Тор                |

| 38      | TC1       | Left   | Right              |

| 40      | TC0       |        | Left               |

#### 5-Wire Touch Panel

The following table describes the wiring for 5-wire resistive touch panels on header J22.

| J22 Pin | Name      | 5-Wire      | 5-Wire (Alternate) |

|---------|-----------|-------------|--------------------|

| 26      | SX-       |             |                    |

| 28      | SY-       |             |                    |

| 30      | SY+       |             |                    |

| 32      | SX+ (TC3) | Lower right | Upper left         |

| 34      | TC4       | Lower left  | Lower left         |

| 36      | TC2       | Wiper       | Wiper              |

| 38      | TC1       | Upper left  | Lower right        |

| 40      | TC0       | Upper right | Upper right        |

#### 8-Wire Touch Panel

The following table describes the wiring for 8-wire resistive touch panels on header J22. This table also includes an example of the wiring from header J22 to an AMT 9546, 8-wire touch screen.

| J22 Pin | Name      | 8-Wire       | AMT 9546 Touch panel |

|---------|-----------|--------------|----------------------|

| 26      | SX-       | Left sense   | 7                    |

| 28      | SY-       | Top sense    | 2                    |

| 30      | SY+       | Bottom sense | 3                    |

| 32      | SX+ (TC3) | Right sense  | 6                    |

| 34      | TC4       | Тор          | 1                    |

| 36      | TC2       | Bottom       | 4                    |

| 38      | TC1       | Left         | 8                    |

| 40      | TC0       | Right        | 5                    |

#### **Backlight**

Most LCDs include one or more cold-cathode fluorescent lamp (CCFL) tubes to backlight the displays. Backlight inverters drive the panel backlights. These circuits are typically external to the display and generate the several hundred volts required to drive the CCFL tubes. Backlights can easily become the greatest source of power consumption in a portable system. To reduce power consumption, applications can dim or turn off the backlighting.

The Catalyst EC supplies software-controlled backlight power and two backlight control signals. Header J22, page 41 includes the backlight signals.

The following table describes the backlight control signals.

| Signal    | J22 Pin | Туре | Description                             |

|-----------|---------|------|-----------------------------------------|

| L_BKLTEN  | 10      | 0    | Turns power to the backlight on or off  |

| L_BKLTCTL | 12      | O-A  | Controls the intensity of the backlight |

For backlight power specifications, see Backlight, page 51.

#### PS/2 Keyboard and Mouse

The Catalyst EC supports a direct connection to a PS/2 mouse and keyboard using the dedicated keyboard/mouse interface of the Super I/O Controller. Connect a PS/2 keyboard to socket J20, page 40 and a PS/2 mouse to socket J21, page 41. For electrical specifications, see Super I/O Controller, page 52.

#### Discrete I/O

To meet the requirement for general-purpose I/O and legacy I/O capabilities, the carrier board includes an I/O expansion port and a Super I/O Controller. The I/O expansion port connects to the Catalyst Module XL SMBus, while the Super I/O Controller connects to the Catalyst Module XL LPC bus. The following sections describe the discrete I/O provided by these devices.

#### I/O Expansion Port

The Catalyst EC includes an I/O expansion port providing sixteen general-purpose inputs and outputs (GPIO) on header J6, page 33. All GPIOs are software-controlled using the SMBus and are programmed as inputs at power up. These GPIOs can generate system interrupts using the SMB ALERT# signal. This capability requires software support.

For electrical specifications, see General-Purpose Inputs and Outputs, page 51.

#### Super I/O Controller

A Super I/O Controller connects to the LPC bus providing system control and three GPIOs. These GPIOs can be used as external interrupts and are available on header J25, page 45.

The following table lists the various discrete I/O controls that are specific to the Catalyst EC.

| GPIO     | Name          | Type | Description                                                           |

|----------|---------------|------|-----------------------------------------------------------------------|

| GP40     | IDE_PATADET   | I    | Indicates that a IDE compatible disk drive is installed in the system |

| GP30     | LVDS_PRESENT# | I    | Indicates that LVDS buffering circuitry is installed in the system    |

| GP60     | LVDS_PDWN#    | 0    | Powers down the LVDS buffers                                          |

| GP62     | CTS4_SIO      | Ю    | GPIO or external interrupt (J25 pin 6)                                |

| GP63     | DCD4_SIO      | Ю    | GPIO or external interrupt (J25 pin 4)                                |

| GP66     | DSR4_SIO      | Ю    | GPIO or external interrupt (J25 pin 5)                                |

| GP36     | H_INIT#       |      |                                                                       |

| GP42     | PCIE_WAKE#    |      |                                                                       |

| CTS5_SIO | Revision bit  | I    | Indicates carrier board revision:<br>Rev 0-3: pulled high             |

| -        |               |      | Rev 4: pulled low                                                     |

The Super I/O Controller's configuration base address is 0x002E. For detailed information about the control of the Super I/O Controller including a memory map, refer to the SMSC SCH3116 datasheet.

# **System Monitoring**

The Super I/O Controller includes temperature sensing, voltage monitoring, and motor or external cooling control. This section describes how the Catalyst EC uses each of these capabilities.

#### **Temperature**

The carrier board includes three temperature sensors that are accessible using the Super I/O Controller hardware monitoring registers. The following table identifies these sensors and their location on the carrier board.

| Sensor         | Location                                              |

|----------------|-------------------------------------------------------|

| Internal       | Internal to the Super I/O Controller                  |

| Remote 1 (Q26) | Component side of the PWB in the power supply section |

| Remote 2 (Q27) | Underside of the PWB under the Super I/O Controller   |

110123-4000A

#### Voltage

Four analog inputs to the Super I/O Controller monitor the on-board voltages as described in the following table.

| Input    | On-board Voltage |

|----------|------------------|

| +12V_MON | VIN              |

| VCCP_IN  | 1.8 V            |

| +2.5V_IN | V3.3S            |

| +5V_IN   | V5S              |

#### **Tachometer**

The Super I/O Controller includes two tachometer inputs and two pulse width modulation (PWM) outputs for motor control or external cooling applications. The Catalyst EC is a low-power device and does not require external cooling. The tachometer inputs and PWM outputs are not supported on the standard Catalyst EC. Contact your local Eurotech technical support if your application requires this function.

#### **Audio Interface**

An Intel High Definition Audio (Intel HD Audio) compatible codec located on the carrier board provides the audio interface for the Catalyst EC. The Catalyst Module XL supports the Intel HD Audio specification implementing high quality audio in an embedded environment. This specification defines a uniform interface between a host computer and audio codec, specifying register control, physical connectivity, programming model, and codec architectural components.

The audio codec supports two stereo line inputs and two stereo line outputs on the carrier board. Stereo jack J12, page 36 provides direct connections to a stereo line input and a stereo line output, while header J13, page 36 connects to a secondary stereo line input and a secondary stereo line output. For electrical specifications, see Audio Interface, page 52.

# **Power and Power Management**

Power management is especially critical in high-performance systems that also require low power dissipation. Handheld and portable systems available today never really turn "off." They make use of power management techniques that cycle the electronics into power saving modes but never fully remove power from the full system. The Catalyst EC includes advanced power management features, including the low-power Atom processor, Advanced Configuration and Power Interface (ACPI) power management, the ability to operate in power-saving modes, and partitioned power distribution.

This section provides an overview of the power supply architecture and summarizes the Catalyst EC power management system. Power regulators on the carrier board accept the main input voltage and generate all other voltages required by the Catalyst Module XL and carrier board circuitry.

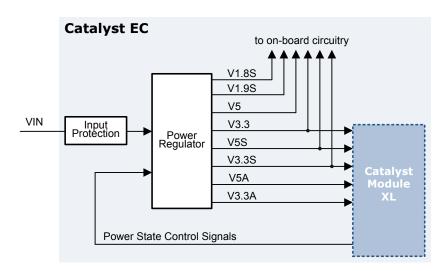

#### **Power Supply Architecture**

The following diagram illustrates the power supply architecture of the Catalyst EC. Notice that voltages ending with an "A" indicate supplies that are always on, while voltages ending with an "S" indicate supplies that are switchable.

The architecture of the power supply partitions power distribution across the Catalyst Module XL and the Catalyst EC carrier board. The Catalyst EC requires a main power input VIN on header J5, page 32. The maximum main input voltage is limited by input protection. Configurations for higher voltage inputs are available as volume production options. For further details, see Power Supply, page 48.

The Catalyst EC can selectively turn off power to various subsystems. This loadshedding feature can significantly reduce power consumption. Applications and the operating system determine how selective power management is utilized.

The following are the subsystems that can be disabled selectively:

- User Interface (LVDS Display, Touch Panel, and Backlight)

- SD/MMC socket

- Wireless module

#### **ACPI Power Management States**

The Catalyst EC supports the ACPI specification. Unlike previous power standards that were BIOS-based, ACPI allows OS-directed power management. It specifies an industry-standard interface for both hardware and software that facilitates power and thermal management. This section describes how the Catalyst EC makes use of the ACPI low power modes.

The ACPI specification defines the low power states for ACPI-compliant systems. The following table describes the states supported by the Catalyst EC.

| State | Mode                | Description                                                                                                                                                                                                                                                         |  |

|-------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| S0    | Full<br>Operation   | All devices are operational with dynamic power management functions active.                                                                                                                                                                                         |  |

| S3    | Standby or<br>Sleep | Most devices are powered down. DRAM is retained using low-power self-refresh. Wake events are active and enable a transition back to full operation.                                                                                                                |  |

| S4    | Hibernation         | All devices are powered down. Operating system context is saved to disk storage prior to powering down system voltage rails. Limited wake events are active. Resume to full operation is dependent on numerous system components including the disk storage device. |  |

| S5    | Power down          | All devices are powered down. The Catalyst Module XL embedded controller is active but may be in low-power mode. No operating system context is preserved. Limited wake events are active.                                                                          |  |

Wake events transition the Catalyst EC from sleep mode back to full operation. Header J25, page 45 includes the signal FWH\_WP# providing an external wake event input. For electrical specifications, see Power Supply, page 48.

Power state signals from the Catalyst Module XL combined with power management circuitry on the carrier board enable transition between these power states. The following table describes the power voltages active in each power state.

| Power State                          | Active Power Rails          | Description                                             |

|--------------------------------------|-----------------------------|---------------------------------------------------------|

| S0 and S3 operation                  | V5, V3.3                    | 5 V and 3.3 V primary supply voltage                    |

| S0 operation                         | V5S, V3.3S,<br>V1.9S, V1.8S | 5 V, 3.3 V, 1.9 V, and 1.8 V power for normal operation |

| S4 and S5 exit & S0 and S3 operation | V5A, V3.3A                  | 5 V and 3.3 V "always" power for up/down circuitry only |

#### Mechanical

The Catalyst EC conforms to the EPIC form factor. This section describes mounting and dimensions of the board.

#### **Mounting Holes**

The carrier board includes three sets of four mounting holes that enable the following mountings:

- Catalyst Module XL to carrier board

- · Disk drive to carrier board

- · Carrier board to enclosure

The mounting holes for the Catalyst Module XL connect electrically to the ground plane, while the mounting holes for the disk drive and carrier board connect electrically to chassis ground. The ground plane and chassis ground are electrically connected. All connections are made using  $0\Omega$  resistors.

Per IPC-A-610D section 4.2.3, secure the board to standoffs using a flat washer against the board with a split washer on top between the flat washer and the screw head or nut. Do not use toothed star washers, as they cut into the plating and laminations of the board over time and will not produce an attachment that will withstand vibration and thermal cycling.

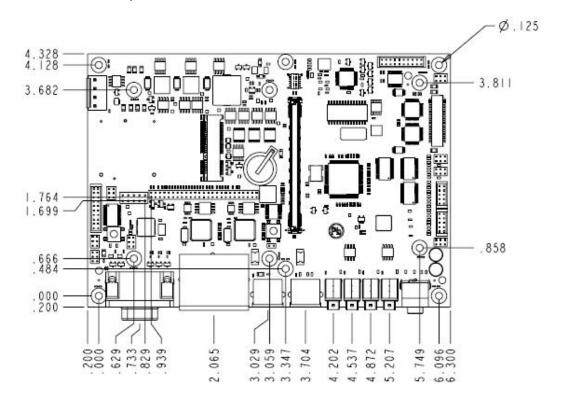

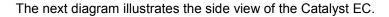

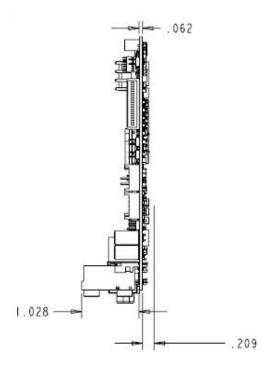

## **Mechanical Drawing**

The following mechanical drawings specify the dimensions of the Catalyst EC, as well as locations of key components on the board. All dimensions are in inches. The first view illustrates the component side of the board.

The final view illustrates the underside of the Catalyst EC. Notice SD/MMC socket J23 is located on the underside.

# Connectors, Switches, Jumpers, and Indicators

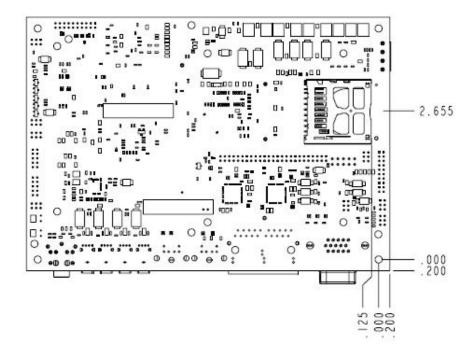

# **Identifying Connectors**

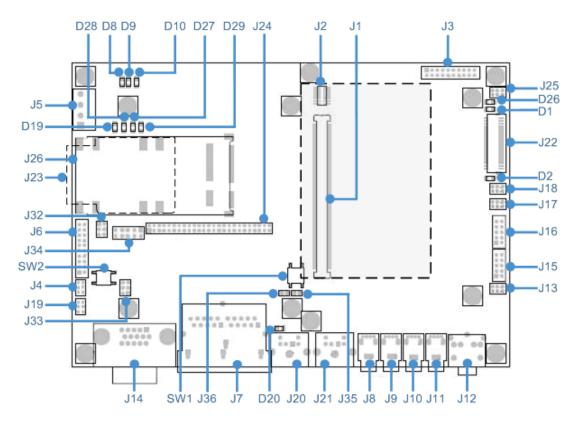

The following diagram illustrates the location of key components on the Catalyst EC. The Catalyst Module XL is located on the right half of the carrier board indicated by a shaded area. Two docking connectors, J1 and J2, lie under the module. Socket J23 is populated on the underside of the carrier board and is indicated with a dashed line border.

# Switches, Jumpers, and Indicators

This section describes various switches, jumpers, and indicators on the carrier board.

#### SW1: Reset

SW1 is the reset button for the Catalyst EC. Pressing SW1 initiates a hardware reset of module circuitry including the processor. Press this button to restart the system without cycling power.

# SW2: On/Off

SW2 is the On/Off button for the Catalyst EC. SW2 turns power used for normal operation on and off or indicates a power state change. This switch also connects to the discrete on/off control signal BTN ONOFF# on header J4, page 32.

#### J35: USB Host/Client Jumper

Type: 2-post header

Jumper J35 selects either USB host or USB client operation on socket J10, page 35.

| Jumper setting | Configuration of J10 |

|----------------|----------------------|

| nc             | USB Host (default)   |

| 1-2            | USB Client           |

#### J36: PCle Multiplexer Jumper

Type: 2-post header

Jumper J36 controls a PCIe port multiplexer included on the Catalyst EC carrier board that selects the Ethernet 1 interface on socket J7, page 33 or the PCIe bus connection on socket J26, page 46.

| Jumper setting | Configuration  |                      |  |

|----------------|----------------|----------------------|--|

|                | J7: Ethernet 1 | J26: PCIe connection |  |

| nc (default)   | Enable         | Disable              |  |

| 1-2            | Disable        | Enable               |  |

#### **Carrier Board LED Indicators**

The carrier board has up to twelve, green light-emitting diodes (LEDs) to indicate system operation. The tables provided in this section describe the LED functionalities.

#### D1: Backlight LED

| LED | Туре  | Description                                     |

|-----|-------|-------------------------------------------------|

| D1  | green | Indicates the backlight enable signal is active |

#### D2: LVDS LED

| LED | Туре  | Description                                    |

|-----|-------|------------------------------------------------|

| D2  | green | Indicates power is applied to the LVDS display |

## D8-D10: Power LEDs

| LED | Туре  | Description                              |

|-----|-------|------------------------------------------|

| D8  | green | Indicates normal operating power (V3.3S) |

| D9  | green | Indicates primary supply voltage (V3.3)  |

| D10 | green | Indicates power is connected (V3.3A)     |

## D19: SD/MMC LED

| LED | Туре  | Description                             |

|-----|-------|-----------------------------------------|

| D19 | green | Indicates activity on the SD/MMC socket |

#### D20: PATA LED

| LED | Туре  | Description                                      |

|-----|-------|--------------------------------------------------|

| D20 | green | Blinking indicates activity on a PATA disk drive |

#### D26: Touch Panel LED

| LED | Туре  | Description                                    |

|-----|-------|------------------------------------------------|

| D26 | green | Blinking indicates activity on the touch panel |

#### D27-D29: Wireless Module LEDs

| LED | Туре  | Description                                     |

|-----|-------|-------------------------------------------------|

| D27 | green | Indicates Wireless Wide Area Network (WWAN)     |

| D28 | green | Indicates Wireless Local Area Network (WLAN)    |

| D29 | green | Indicates Wireless Personal Area Network (WPAN) |

#### D30: Embedded USB Mass Storage LED (optional)

| LED | Туре  | Description                                      |

|-----|-------|--------------------------------------------------|

| D30 | green | Blinking indicates activity on the USB interface |

#### **Ethernet LEDs**

The dual Ethernet socket J7 integrates two LEDs with each RJ-45 socket. The LED on the left side indicates speed as described in the following table.

| Color  | Speed (Mbps) |  |

|--------|--------------|--|

| Green  | 1000         |  |

| Yellow | 100          |  |

| Off    | 10           |  |

The green LED on the right side indicates connection and activity as described in the following table.

| Operation | Link/Activity     |  |

|-----------|-------------------|--|

| On        | Valid connection  |  |

| Blinking  | Ethernet activity |  |

| Off       | No connection     |  |

# **Signal Headers**

The following tables describe the electrical signals available on the connectors of the carrier board. Each section provides relevant details about the connector including part numbers, mating connectors, signal descriptions, and references to related sections.

For the location of the connectors, see Identifying Connectors, page 28.

#### J1: Docking Connector: Data

The Catalyst Module XL connector J1 mates to the carrier board connector J1. Most data signals are provided on this docking connector.

#### J2: Docking Connector: Power

The Catalyst Module XL receives the power input and controls for interfacing with an external power supply on this docking connector.

#### J3: JTAG

Board connector: 2x10 socket, 2 mm, Hirose DF11-20DP-2DSA

The Catalyst EC includes a JTAG interface for factory test and for board-level software debugging; otherwise, the JTAG port is not supported for application use.

| Pin | Name       | Туре | Description     |

|-----|------------|------|-----------------|

| 1   | JTAG_TRST# | 1    |                 |

| 2   | GND        | Р    |                 |

| 3   | JTAG_TDI   | 1    |                 |

| 4   | GND        | Р    |                 |

| 5   | JTAG_TDO   | 0    |                 |

| 6   | GND        | Р    |                 |

| 7   | JTAG_TMS   | 1    |                 |

| 8   | GND        | Р    |                 |

| 9   | JTAG_TCK   | 1    |                 |

| 10  | GND        | Р    | JTAG interface  |

| 11  | ATE_GPIO1  | IO   | JTAG IIIterrace |

| 12  | GND        | Р    |                 |

| 13  | ATE_GPIO2  | IO   |                 |

| 14  | GND        | Р    |                 |

| 15  | ATE_GPIO3  | IO   |                 |

| 16  | GND        | Р    |                 |

| 17  | MON_3.3VAO | PO   |                 |

| 18  | GND        | Р    |                 |

| 19  | MON_5VAO   | PO   |                 |

| 20  | GND        | Р    |                 |

#### J4: Maintenance Port

Board connector: 2x3 header, 2 mm, Samtec TMM-103-03-T-D

Header J4 provides an EIA-232 serial port for the Catalyst Module XL embedded controller. This maintenance port is not supported for application use. It is intended for reprogramming the embedded controller, troubleshooting, and software debug. For additional information about using this port, see Appendix E – Maintenance Port, page 60.

The signal BTN\_ONOFF# connects to J4 and to switch SW2, page 28. This signal controls power on/off or indicates a power state change. For electrical specifications, see Power Supply, page 48.

| Pin | Name       | Type | Description   |

|-----|------------|------|---------------|

| 1   | DEBUG_TX   | 0    | Transmit Data |

| 2   | DEBUG_RX   | I    | Receive Data  |

| 3   | BTN_ONOFF# | I-5  | Power on/off  |

| 4   | GND        | Р    | ground        |

| 5   | GND        | Р    | ground        |

| 6   | GND        | Р    | ground        |

#### J5: Power Input

Board connector: 4-pin header, 0.156 inch, Tyco Electronics 1-1318300-4

Mating connector: plug housing, Tyco Electronics 1-1123722-4 and crimp pins, Tyco Electronics 1318912-1

Header J5 accepts input power from an external supply. VIN is the main power input to the Catalyst EC. Power regulators on the carrier board accept a 12 V main input voltage and generate all other voltages required by the Catalyst Module XL and carrier board circuitry. For details about the power supply architecture, see Power Supply Architecture, page 24.

| Pin | Name | Туре       | Description                |

|-----|------|------------|----------------------------|

| 1   | OND  | Б          | anaad                      |

| 2   | GND  | Р          | ground                     |

| 3   | VIN  | PI         | 12 V (nominal) newer input |

| 4   | VIIN | <b>7</b> 1 | 12 V (nominal) power input |

Disconnect the power input before removing the Catalyst Module XL. Removing the module from a powered carrier board may result in damage to both the carrier board and to the module.

#### J6: GPIO

Board connector: 2x10 header, 2 mm, Hirose DF11-20DP-2DSA

Mating connector: Hirose DF11 series socket

The Catalyst EC includes sixteen GPIO signals on header J6. For further details, see I/O Expansion Port, page 21.

| Pin | Name   | Туре     | Description      |

|-----|--------|----------|------------------|

| 1   | V5S    | PO       | 5 V power output |

| 2   |        |          |                  |

| 3   | GPIO0  | IO-LVTTL |                  |

| 4   | GPIO1  | IO-LVTTL |                  |

| 5   | GPIO2  | IO-LVTTL |                  |

| 6   | GPIO3  | IO-LVTTL | GPIO             |

| 7   | GPIO4  | IO-LVTTL | GFIO             |

| 8   | GPIO5  | IO-LVTTL |                  |

| 9   | GPIO6  | IO-LVTTL |                  |

| 10  | GPIO7  | IO-LVTTL |                  |

| 11  | GND    | Р        | ground           |

| 12  | GND    | Г        | ground           |

| 13  | GPIO8  | IO-LVTTL |                  |

| 14  | GPIO9  | IO-LVTTL |                  |

| 15  | GPIO10 | IO-LVTTL |                  |

| 16  | GPIO11 | IO-LVTTL | CDIC             |

| 17  | GPIO12 | IO-LVTTL | GPIO             |

| 18  | GPIO13 | IO-LVTTL |                  |

| 19  | GPIO14 | IO-LVTTL |                  |

| 20  | GPIO15 | IO-LVTTL |                  |

#### J7: Ethernet 0 and Ethernet 1

Board connector: dual RJ-45 socket with LEDs

Mating connector: RJ-45 plug

Socket J7 is a dual RJ-45 type that provides up to two 10/100/1000 Mbps Ethernet ports with indicators and built-in magnetics included for each Ethernet connection. The connector shield is tied to chassis ground. For further details, see Ethernet, page 16.

Note: Ethernet 1 is mutually exclusive with the PCIe bus connection on socket J26. To enable Ethernet 1 and disconnect the PCIe bus, do not install jumper J36, page 29.

#### J8: USB Host 0

Board connector: USB Type A receptacle, Molex 89485-8000

Mating connector: USB Type A plug

Socket J8 provides a general-purpose USB 2.0 host port. The connector shield is tied to chassis ground. For further details, see Universal Serial Bus, page 14.

| Pin | Name          | Туре | Description         |

|-----|---------------|------|---------------------|

| 1   | USB_HOST0_PWR | РО   | 5 V DC power output |

| 2   | USB_HOST0-    | 10   | LICD Heat 0         |

| 3   | USB_HOST0+    | Ю    | USB Host 0          |

| 4   | GND           | Р    | ground              |

#### J9: USB Host 1

Board connector: USB Type A receptacle, Molex 89485-8000

Mating connector: USB Type A plug

Socket J9 provides a general-purpose USB 2.0 host port. The connector shield is tied to chassis ground. For further details, see Universal Serial Bus, page 14.

| Pin | Name          | Туре | Description         |

|-----|---------------|------|---------------------|

| 1   | USB_HOST1_PWR | РО   | 5 V DC power output |

| 2   | USB_HOST1-    | 10   | LICD Heat 4         |

| 3   | USB_HOST1+    | Ю    | USB Host 1          |

| 4   | GND           | Р    | ground              |

#### J10: USB Host 2 or USB Client

Board connector: USB Type A receptacle, Molex 89485-8000

Mating connector: USB Type A plug

The USB signals on socket J10 support a USB host or USB client port. Jumper J35, page 29 selects the operation of this port. The connector shield is tied to chassis ground. For further details, see Universal Serial Bus, page 14.

|     |               | Description |                       |             |  |

|-----|---------------|-------------|-----------------------|-------------|--|

| Pin | Name          | Туре        | USB Host<br>(default) | USB Client  |  |

| 1   | USB_HOST2_PWR | PO          | 5 V DC output         | nc          |  |

| 2   | USB_HOST2-    | 10          | USB Host 2            | LICD Client |  |

| 3   | USB_HOST2+    | Ю           | USB HUSI Z            | USB Client  |  |

| 4   | GND           | Р           | ground                | ground      |  |

Warning: Socket J10 pin 1 is a power output in USB host operation. Check the setting of jumper J35 before connecting a USB device to this port.

#### J11: USB Host 3

Board connector: USB Type A receptacle, Molex 89485-8000

Mating connector: USB Type A plug

Socket J11 provides a general-purpose USB 2.0 host port. The connector shield is tied to chassis ground. For further details, see Universal Serial Bus, page 14.

| Pin | Name          | Туре | Description         |

|-----|---------------|------|---------------------|

| 1   | USB_HOST3_PWR | РО   | 5 V DC power output |

| 2   | USB_HOST3-    | 10   | LICD Heat 2         |

| 3   | USB_HOST3+    | Ю    | USB Host 3          |

| 4   | GND           | Р    | ground              |

#### J12: Stereo Line Out 0 and Stereo Line In 0

Board connector: dual stack stereo jack, 3.5 mm, CUI Inc SJD-3510-45

Mating connector: 3.5 mm stereo plug

The audio codec included on the carrier board provides two audio inputs and two audio outputs on stereo jack J12 and header J13.

Stereo jack J12 provides direct connections to a stereo line input and a stereo line output. The line out is wired to the upper socket of the dual stack, while the line in is wired to the lower socket. The diagram at the right illustrates stereo jack J12. In the following table, pins in the upper socket are indicated by a "U" and pins in the lower socket are indicated by an "L".

For further details, see Audio Interface, page 23.

| Pin | Name        | Туре | Description               |

|-----|-------------|------|---------------------------|

| 1U  | LINE_OUT0_R | AO   | Line Out 0, right channel |

| 3U  | nc          |      |                           |

| 4U  | LINE_OUT0_L | AO   | Line Out 0, left channel  |

| 5U  | GND_HDA     | Р    | HD Audio ground           |

| 1L  | LINE_IN0_R  | Al   | Line In 0, right channel  |

| 2L  | nc          |      |                           |

| 3L  | nc          |      |                           |

| 4L  | LINE_IN0_L  | Al   | Line In 0, left channel   |

| 5L  | GND_HDA     | Р    | HD Audio ground           |

#### J13: Stereo Line Out 1 and Stereo Line In 1

Board connector: 2x3 header, 2 mm, Samtec TMM-103-03-T-D

Mating connector: Samtec TCSD series socket

The audio codec included on the carrier board provides two audio inputs and two audio outputs on stereo jack J12 and header J13. Header J13 provides the connections to a secondary stereo line input and a secondary stereo line output. For further details, see Audio Interface, page 23.

| Pin | Name        | Туре | Description               |

|-----|-------------|------|---------------------------|

| 1   | LINE_IN1_R  | ΑI   | Line In 1, right channel  |

| 2   | GND_HDA     | Р    | HD Audio ground           |

| 3   | LINE_IN1_L  | ΑI   | Line In 1, left channel   |

| 4   | LINE_OUT1_L | AO   | Line Out 1, left channel  |

| 5   | GND_HDA     | Р    | HD Audio ground           |

| 6   | LINE_OUT1_R | AO   | Line Out 1, right channel |

## J14: Analog RGB

Board connector: high-density 15-pin D-sub connector, Tyco Electronics 1734530-3

Mating connector: high-density 15-pin D-sub plug

The Catalyst EC drives an analog RGB display using a direct connection to J14. This interface supports an 8:8:8 RGB port and DDC bus that is used to identify the type of monitor connected. The connector shield is tied to chassis ground. For further details, see Analog RGB, page 19.

| Pin | Name      | Type | Description                |

|-----|-----------|------|----------------------------|

| 1   | VGA_RED   | AO   | Red data                   |

| 2   | VGA_GREEN | AO   | Green data                 |

| 3   | VGA_BLUE  | AO   | Blue data                  |

| 4   | nc        |      |                            |

| 5   | GND       | Р    | ground                     |

| 6   | GND       | Р    | ground                     |

| 7   | GND       | Р    | ground                     |

| 8   | GND       | Р    | ground                     |

| 9   | nc        |      |                            |

| 10  | GND       | Р    | ground                     |

| 11  | nc        |      |                            |

| 12  | DDC_DATA  | IO-5 | DDC I <sup>2</sup> C data  |

| 13  | VGA_HSYNC | AO   | Horizontal sync            |

| 14  | VGA_VSYNC | AO   | Vertical sync              |

| 15  | DDC_CLK   | O-5  | DDC I <sup>2</sup> C clock |

### J15: Serial 1

Board connector: 2x5 header, 2 mm, Hirose DF11-10DP-2DSA

Mating connector: Hirose DF11 series socket

Header J15 supports a full-feature EIA-232 serial port. For further details, see Serial Ports, page 14.

| Pin | Name     | Туре | Description           |

|-----|----------|------|-----------------------|

| 1   | DCD1     | 1    | Data Carrier Detect 1 |

| 2   | RXD1     | I    | Receive Data 1        |

| 3   | TXD1     | 0    | Transmit Data 1       |

| 4   | DTR1     | 0    | Data Terminal Ready 1 |

| 5   | GND_COM1 | Р    | ground                |

| 6   | DSR1     | 1    | Data Set Ready 1      |

| 7   | RTS1     | 0    | Request To Send 1     |

| 8   | CTS1     | 1    | Clear To Send 1       |

| 9   | RIB1     | I    | Ring Indicator 1      |

| 10  | GND_COM1 | Р    | ground                |

#### J16: Serial 2

Board connector: 2x5 header, 2 mm, Hirose DF11-10DP-2DSA

Mating connector: Hirose DF11 series socket

Header J16 supports a full-feature EIA-232 serial port. For further details, see Serial Ports, page 14.

| Pin | Name     | Туре | Description           |

|-----|----------|------|-----------------------|

| 1   | DCD2     | I    | Data Carrier Detect 2 |

| 2   | RXD2     | I    | Receive Data 2        |

| 3   | TXD2     | 0    | Transmit Data 2       |

| 4   | DTR2     | 0    | Data Terminal Ready 2 |

| 5   | GND_COM2 | Р    | ground                |

| 6   | DSR2     | I    | Data Set Ready 2      |

| 7   | RTS2     | 0    | Request To Send 2     |

| 8   | CTS2     | I    | Clear To Send 2       |

| 9   | RIB2     | I    | Ring Indicator 2      |

| 10  | GND_COM2 | Р    | ground                |

38 ) 110123-4000A

#### J17: Serial 3

Board connector: 2x3 header, 2 mm, Samtec TMM-103-03-T-D

Mating connector: Samtec TCSD series socket

Header J17 supports a serial port that can be configured for EIA-232 or EIA-422/485 operation. The input signal MODE3 selects EIA-232 or EIA-422/485 mode. This input is pulled up on a standard Catalyst EC defaulting to EIA-422/485 mode. To convert to EIA-232 mode, connect this input to ground. For further details, see Serial Ports, page 14.

| Pin | Name     | Type | EIA-422/485 (default)         | EIA-232           |

|-----|----------|------|-------------------------------|-------------------|

| 1   | RX3+     | 1    | Non-inverting Receive Data 3  |                   |

| 2   | RX3-     | 1    | Inverting Receive Data 3      | Receive Data 3    |

| 3   | COM_GND3 | Р    | ground                        | ground            |

| 4   | MODE3    | I    | NC                            | GND               |

| 5   | TX3+     | Ο    | Non-inverting Transmit Data 3 | Request To Send 3 |

| 6   | TX3-     | Ο    | Inverting Transmit Data 3     | Transmit Data 3   |

#### J18: Serial 4

Board connector: 2x3 header, 2 mm, Samtec TMM-103-03-T-D

Mating connector: Samtec TCSD series socket

Header J18 supports a serial port that can be configured for EIA-232 or EIA-422/485 operation. The input signal MODE4 selects EIA-232 or EIA-422/485 mode. This input is pulled up on a standard Catalyst EC defaulting to EIA-422/485 mode. To convert to EIA-232 mode, connect this input to ground. For further details, see Serial Ports, page 14.

| Pin | Name     | Туре | EIA-422/485 (default)         | EIA-232           |

|-----|----------|------|-------------------------------|-------------------|

| 1   | RX4+     | I    | Non-inverting Receive Data 4  |                   |

| 2   | RX4-     | I    | Inverting Receive Data 4      | Receive Data 4    |

| 3   | COM_GND4 | Р    | ground                        | ground            |

| 4   | MODE4    | I    | NC                            | GND               |

| 5   | TX4+     | 0    | Non-inverting Transmit Data 4 | Request To Send 4 |

| 6   | TX4-     | 0    | Inverting Transmit Data 4     | Transmit Data 4   |

#### J19: Serial 5 and Wireless Module Power Control

Board connector: 2x3 header, 2 mm, Samtec TMM-103-03-T-D

Mating connector: Samtec TCSD series socket

Header J19 supports a 3-wire serial port at LVTTL levels and includes a 2-pin jumper for controlling the power sequencing on the wireless module socket J26, page 46. For further details, see Serial Ports, page 14 and Wireless Module, page 15, respectively.

| Pin | Name      | Туре    | Description                   |

|-----|-----------|---------|-------------------------------|

| 1   | TX5       | O-LVTTL | Transmit Data 5               |

| 2   | RX5       | I-LVTTL | Receive Data 5                |

| 3   | COM_GND5  | Р       | ground                        |

| 4   | SLOT1_CD# |         |                               |

| 5   | PWR_SW    |         | Wireless madule nouse control |

| 6   | PWR_PU    |         | Wireless module power control |

Wireless Module Power Control Jumper

Header J19 includes a 2-pin jumper that controls the power sequencing to the wireless module socket J26, as shown in the following table.

| Header J19 Pin | Power Sequencing  |

|----------------|-------------------|

| 5-6            | Enable            |

| nc             | Disable (default) |

#### J20: PS/2 Keyboard

Board connector: 6-pin mini-DIN socket, MDJ-104-6PS

Mating connector: mini-DIN plug

The Catalyst EC supports a PS/2 keyboard on socket J20. The 5 V power output supplied on this socket includes a 0.5 A fuse. The connector shield is tied to chassis ground. For a description of the PS/2 keyboard port, see PS/2 Keyboard and Mouse, page 21.

| Pin | Name     | Туре | Description         |

|-----|----------|------|---------------------|

| 1   | KBD_DATA | 0    | PS/2 keyboard data  |

| 2   | nc       |      |                     |

| 3   | GND      | Р    | ground              |

| 4   | 5V_KBD   | РО   | 5 V power output    |

| 5   | KBD_CLK  | 0    | PS/2 keyboard clock |

| 6   | nc       |      |                     |

40 \ 110123-4000A

#### J21: PS/2 Mouse

Board connector: 6-pin mini-DIN socket, MDJ-104-6PS

Mating connector: mini-DIN plug

The Catalyst EC supports a PS/2 mouse on socket J21. The 5 V power output supplied on this socket includes a 0.5 A fuse. The connector shield is tied to chassis ground. For a description of the PS/2 mouse port, see PS/2 Keyboard and Mouse, page 21.

| Pin | Name     | Туре | Description      |

|-----|----------|------|------------------|

| 1   | MSE_DATA | 0    | PS/2 mouse data  |

| 2   | nc       |      |                  |

| 3   | GND      | Р    | ground           |

| 4   | 5V_MSE   | РО   | 5 V power output |

| 5   | MSE_CLK  | 0    | PS/2 mouse clock |