## **DESIGN-IN GUIDE**

Rev 5 – September 2011 – 110125-10005

www.eurotech.com

## Trademarks

All trademarks both marked and not marked appearing in this document are the property of their respective owners.

# **Document Revision History**

| REVISION | DESCRIPTION         | DATE      |

|----------|---------------------|-----------|

| 3        | Preliminary release | Aug 2010  |

| 4        | Appendix D removed  | Oct 2010  |

| 5        | Initial release     | Sept 2011 |

# **Table of Contents**

| Trademarks                                       |  |

|--------------------------------------------------|--|

| Document Revision History                        |  |

| Table of Contents                                |  |

| Important User Information                       |  |

| Safety Notices and Warnings                      |  |

| Life Support Policy                              |  |

| Warranty                                         |  |

| WEEE                                             |  |

| RoHS                                             |  |

| Technical Assistance                             |  |

| Conventions                                      |  |

| Product Overview                                 |  |

| Block Diagram                                    |  |

| Features                                         |  |

| Design Checklist                                 |  |

| Development Kit                                  |  |

| Related Documents                                |  |

| Software Specifications                          |  |

| Operating System Support                         |  |

| BIOS                                             |  |

| Software Development Kit                         |  |

| Everyware <sup>™</sup> Software Framework        |  |

| Hardware Specifications                          |  |

| Core Processor                                   |  |

| Intel Atom Processor                             |  |

| Intel I/O Controller Hub<br>Embedded Controller  |  |

| Trusted Platform Management (option)             |  |

| Memory                                           |  |

| Synchronous DRAM                                 |  |

| Non-Volatile Memory                              |  |

| Flash SSD (option)<br>External Memory Interfaces |  |

| Communications                                   |  |

| PCI Express                                      |  |

| USB                                              |  |

| Gigabit Ethernet<br>Carrier I <sup>2</sup> C Bus |  |

| System Management Bus                            |  |

| Display and User Interface                       |  |

| LVDS Display and Backlight Control               |  |

| VGA Display                                      |  |

| Inputs and Outputs<br>Low Pin Count Bus          |  |

| Reset Signals                                    |  |

| General-Purpose Input and Output                 |  |

| Intel High Definition Audio                      | . 23 |

|--------------------------------------------------|------|

| Power Requirements                               |      |

| Low Power States                                 |      |

| Power Supply Architecture<br>Power State Signals |      |

| -                                                |      |

| Mechanical Specifications                        |      |

| Mechanical Design                                |      |

| Mechanical Drawing                               |      |

| Total Stack Height<br>Mounting Holes             |      |

| Insertion and Removal                            |      |

| Thermal Management                               |      |

| Carrier Board Design                             |      |

| •                                                |      |

| Design Guidelines Design Constraints             |      |

| EMI/RFI Protection                               |      |

| <br>Routing Guidelines                           |      |

| Power Planes                                     | . 37 |

| Requirements and Recommendations                 | . 37 |

| Test and Debug                                   | . 38 |

| Connectors                                       | 39   |

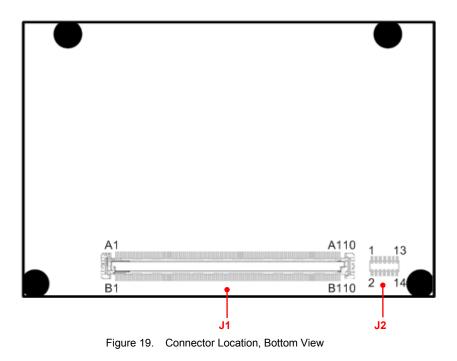

| Identifying Connectors                           |      |

| Signal Headers                                   |      |

| J1: Docking Connector: Data                      |      |

| J2: Docking Connector: Power                     |      |

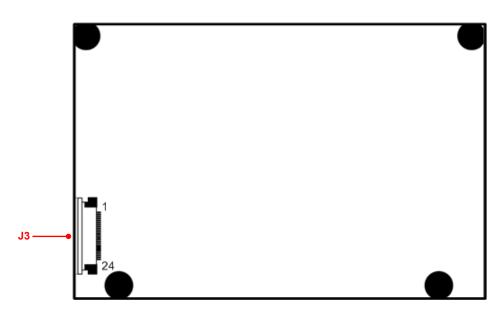

| J3: ITP Debug Port                               |      |

| System Specifications                            | 45   |

| Power                                            |      |

| Power Supply                                     |      |

| Power Consumption                                |      |

| Performance                                      |      |

| Electrical                                       |      |

| Reset Signals                                    |      |

| PCIe Clock Generator                             | . 47 |

| USB                                              |      |

| Carrier I <sup>2</sup> C Bus                     |      |

| SMBus                                            |      |

| LVDS Display and Backlight<br>VGA Display        |      |

| General-purpose Inputs and Outputs               |      |

| Intel High Definition Audio                      |      |

| General                                          | . 49 |

| Crystal Frequencies                              | . 49 |

| Real-Time Clock                                  | . 50 |

| Environmental                                    | . 50 |

| Appendix A – Reference Information               | . 51 |

| Appendix B – Board Revision                      | . 52 |

| Eurotech Worldwide Presence                      | . 53 |

# **Important User Information**

In order to lower the risk of personal injury, electric shock, fire, or equipment damage, users must observe the following precautions as well as good technical judgment, whenever this product is installed or used.

All reasonable efforts have been made to ensure the accuracy of this document; however, Eurotech assumes no liability resulting from any error/omission in this document or from the use of the information contained herein.

Eurotech reserves the right to revise this document and to change its contents at any time without obligation to notify any person of such revision or changes.

## **Safety Notices and Warnings**

The following general safety precautions must be observed during all phases of operation, service, and repair of this equipment. Failure to comply with these precautions or with specific warnings elsewhere in this manual violates safety standards of design, manufacture, and intended use of the equipment. Eurotech assumes no liability for the customer's failure to comply with these requirements.

The safety precautions listed below represent warnings of certain dangers of which Eurotech is aware. You, as the user of the product, should follow these warnings and all other safety precautions necessary for the safe operation of the equipment in your operating environment.

### Installation in Enclosures

In the event that the product is placed within an enclosure, together with other heat generating equipment, ensure proper ventilation.

### Do Not Operate in an Explosive Atmosphere

Do not operate the equipment in the presence of flammable gases or fumes. Operation of any electrical equipment in such an environment constitutes a definite safety hazard.

## Alerts that can be found throughout this manual

The following alerts are used within this manual and indicate potentially dangerous situations.

#### Danger, electrical shock hazard:

Information regarding potential electrical shock hazards:

- Personal injury or death could occur. Also damage to the system, connected peripheral devices, or software could occur if the warnings are not carefully followed.

- Appropriate safety precautions should always be used, these should meet the requirements set out for the environment that the equipment will be deployed in.

#### Warning:

Information regarding potential hazards:

- Personal injury or death could occur. Also damage to the system, connected peripheral devices, or software could occur if the warnings are not carefully followed.

- Appropriate safety precautions should always be used, these should meet the requirements set out for the environment that the equipment will be deployed in.

#### Information and/or Notes:

These will highlight important features or instructions that should be observed.

### Use an Appropriate Power Supply

- Only start the product with a power supply that conforms to the voltage requirements as specified in Power Supply, page 45. In case of uncertainty about the required power supply, please contact your local Eurotech Technical Support Team.

- Use power supplies that are compliant with SELV regulation.

- Avoid overcharging power-points.

### Antistatic Precautions

To avoid damage caused by ESD (Electro Static Discharge), always use appropriate antistatic precautions when handing any electronic equipment.

## Life Support Policy

Eurotech products are not authorized for use as critical components in life support devices or systems without the express written approval of Eurotech.

## Warranty

For Warranty terms and conditions users should contact their local Eurotech Sales Office. See Eurotech Worldwide Presence, page 53 for full contact details.

## WEEE

The information below is issued in compliance with the regulations as set out in the 2002/96/EC directive, subsequently superseded by 2003/108/EC. It refers to electrical and electronic equipment and the waste management of such products. When disposing of a device, including all of its components, subassemblies, and materials that are an integral part of the product, you should consider the WEEE directive.

This device is marketed after August 13, 2005 and you must separate all of its components when possible and dispose of them in accordance with local waste disposal legislations.

- Because of the substances present in the equipment, improper use or disposal of the refuse can cause damage to human health and to the environment.

- With reference to WEEE, it is compulsory not to dispose of the equipment with normal urban refuse and arrangements should be instigated for separate collection and disposal.

- Contact your local waste collection body for more detailed recycling information.

- In case of illicit disposal, sanctions will be levied on transgressors.

## RoHS

This device, including all its components, subassemblies and the consumable materials that are an integral part of the product, has been manufactured in compliance with the European directive 2002/95/EC known as the RoHS directive (Restrictions on the use of certain Hazardous Substances). This directive targets the reduction of certain hazardous substances previously used in electrical and electronic equipment (EEE).

## **Technical Assistance**

If you have any technical questions, cannot isolate a problem with your device, or have any enquiry about repair and returns policies, contact your local Eurotech Technical Support Team.

See Eurotech Worldwide Presence, page 53 for full contact details.

## Transportation

When transporting any module or system, for any reason, it should be packed using anti-static material and placed in a sturdy box with enough packing material to adequately cushion it.

#### Warning:

Any product returned to Eurotech that is damaged due to inappropriate packaging will not be covered by the warranty.

## **Conventions**

The following table describes the conventions for signal names used in this document.

| Convention | Explanation                          |  |

|------------|--------------------------------------|--|

| GND        | Digital ground plane                 |  |

| #          | ctive low signal                     |  |

| + or P     | Positive signal in differential pair |  |

| - or N     | Negative signal in differential pair |  |

The following table describes the abbreviations for direction and electrical characteristics of a signal used in this document.

| Туре     | Explanation                         |  |

|----------|-------------------------------------|--|

| 1        | Signal is an input to the system    |  |

| 0        | Signal is an output from the system |  |

| 10       | Signal may be input or output       |  |

| Р        | Power and ground                    |  |

| Α        | Analog signal                       |  |

| OD       | Open-drain                          |  |

| CMOS     | 3.3 V CMOS                          |  |

| LVCMOS   | 1.05 V CMOS                         |  |

| LVTTL    | Low Voltage TTL                     |  |

| 3.3      | 3.3 V signal level                  |  |

| 5        | 5 V signal level                    |  |

| IDE      | 5 V tolerant signal                 |  |

| HDA      | High Definition Audio, 3.3 V signal |  |

| LVDS     | Low Voltage Differential Signalling |  |

| PCle     | PCI Express signal                  |  |

| SATA     | SATA differential signal            |  |

| NC       | No Connection                       |  |

| Reserved | Use is reserved to Eurotech         |  |

Some signals include termination on the Catalyst LP. The following table describes the abbreviations that specify the signal termination.

| Termination | Explanation                               |  |

|-------------|-------------------------------------------|--|

| PU          | Pull-up resistor to the specified voltage |  |

| PD          | Pull-down resistor                        |  |

| R           | Series resistor                           |  |

| C           | Series capacitor                          |  |

# **Product Overview**

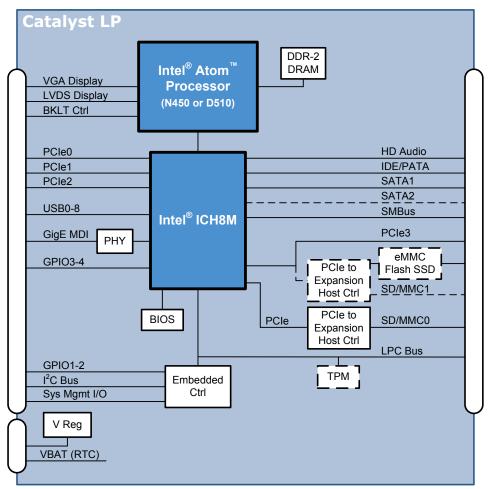

The Catalyst LP is a high-performance module based on the Intel<sup>®</sup> Atom<sup>™</sup> processor N450 (single core) or Intel<sup>®</sup> Atom<sup>™</sup> processor D510 (dual core). It uses an integrated two-chip solution comprised of the Intel Atom processor and Intel<sup>®</sup> I/O Controller Hub (Intel<sup>®</sup> ICH8M). The Intel Atom processor contains an integrated 2D/3D graphics engine supporting hardware-accelerated graphics display and video processing capabilities, while the Intel ICH8M supports extensive I/O and data storage capabilities. The Catalyst LP maximizes the performance capabilities of the Intel Atom processor offering a feature-dense embedded solution.

An application-specific carrier board integrates with the Catalyst LP for a total production solution. This flexible, modular architecture enables easy customization and quick time-to-market. A Eurotech carrier board is available that implements several industry-standard interfaces allowing development across a broad spectrum of end-use applications.

The Catalyst LP is available with a variety of operating systems. Support is also available for the Java Virtual Machine and Eurotech's Everyware<sup>™</sup> Software Framework, which offers an easy-to-use, Javabased development environment that minimizes time to market and allows for easy portability for future expansion.

## **Block Diagram**

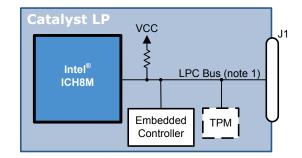

The following diagram illustrates the system organization of the Catalyst LP. Notice that the data connector has been divided into two sections for this illustration. Dotted lines indicate options.

## **Features**

## Processor

- Intel<sup>®</sup> Atom<sup>™</sup> processor N450 (single core) or Intel<sup>®</sup> Atom<sup>™</sup> processor D510 (dual core)

- 200 MHz graphics engine (single core) or 400 MHz graphics engine (dual core)

- Intel<sup>®</sup> I/O Controller Hub (Intel<sup>®</sup> ICH8M)

## Integrated System Functions

- Embedded Controller

- Optional Trusted Platform Management (Contact Eurotech for details)

## Memory

- Up to 2 GB DDR-2 DRAM

- Optional on-board eMMC flash SSD (Contact Eurotech for details)

- Integrated system BIOS

- Battery-backed real-time clock

- External memory support

- IDE/PATA disk drive

- $_{\odot}$  SATA disk drive

- USB disk drive

- SD/MMC card

- $_{\odot}$  PCI Express card

## Communications

- Up to four PCI Express one lane slots

- Custom configuration option for one PCI Express four lane slot

- Nine USB 2.0 ports operating at low, full, and high speeds

- Gigabit Ethernet with physical layer transceiver

- I<sup>2</sup>C bus with I<sup>2</sup>C master device

- System Management Bus

## User Interface and Display

- Independent LVDS display output and VGA display output

- Backlight interface with control signals for intensity and power

## **Inputs and Outputs**

- Low Pin Count bus for general-purpose I/O expansion

- · Four general-purpose inputs and outputs

## Audio Interface

• Intel<sup>®</sup> High Definition Audio supporting up to two external audio codecs

## **Power Supply**

- 3.3 V and 5 V main power inputs

- ACPI power management

## Mechanical

- 67 mm x 100 mm dimensions

- · Less than 10 mm total stack height

## **Design Checklist**

Eurotech provides a host of services to ensure that your product is up and running from the first prototype release. We recommend the following process for every Catalyst LP carrier board design:

## Kickoff Stage

During the Kickoff Stage, you will develop your block diagram and identify any customizations your application may require.

#### **Gather your reference materials**

Eurotech provides several documents that include key information for designing a custom carrier board. Use the following resources and ask questions:

- Catalyst LP Design-In Guide

- Catalyst LP Development Kit User Manual

- Carrier Board Routing Guidelines

- 3D CAD models

- Reference Carrier Board Schematic

- Reference Carrier Board Bill of Materials

#### Define your requirements

Define your system's requirement. Be sure to include requirements such as the product features, the input power, the type of transient protection on the power supply, connectivity to the module, and all I/O to your system.

#### Create a block diagram

Create a block diagram of your proposed design. This step helps to formulate the best way to connect different devices to the module.

#### □ Identify customizations

Identify any customizations that your application requires. Examples of customizations are custom LCD panel timings and backlight control, custom module configurations, or supporting a device that is not included on Eurotech's standard carrier board. Customizations may require updates to the BIOS.

### Utilize the Catalyst LP Development Kit

Utilize the Catalyst LP Development Kit for validating your proposed design. For example, if a USB device is to be used on USB port 6, test that device by connecting it to USB port 6 on the Catalyst LP Development Kit. This testing also allows you to validate your OS image with all required drivers loaded.

#### □ Kickoff review

Early in the development of your carrier board, meet with your Eurotech representative to review your block diagram and discuss customizations. Incorporate any changes into your design.

## Preliminary Design Stage

During the Preliminary Design Stage, you will finalize your block diagram, agree on customizations, and begin your preliminary schematic.

#### □ Use the reference schematic

Use Eurotech's reference carrier board schematic as a starting point for your design. This schematic includes many commonly used interfaces. Using the same connectivity to the module will minimize the time spent in debugging your design.

#### □ Select components from the reference bill of materials

Select the same components as those used in Eurotech's reference carrier board bill of materials. Eurotech selects components that are optimized for embedded systems based on quality, low-power consumption, availability, reliability, and industrial temperature options. Selecting the same components also allows you to use the drivers Eurotech has already integrated with the OS builds.

#### □ Follow the design requirements and recommendations

Follow the design requirements and recommendations listed in Carrier Board Design, page 35 of this design-in guide. This section provides details about circuitry to include on the carrier board.

#### Preliminary design review

Stay in contact with your Eurotech representative during your preliminary design. Together, finalize your block diagram and agree on customizations needed. Continue to ask questions as you move towards finalizing your design.

#### Critical Design Stage

During the Critical Design Stage, you will finalize your schematic making sure that you have met all the module's electrical, thermal, and mechanical design requirements.

#### Implement power supply sequencing

Implement the exact power supply sequencing described in Power State Signals, page 27 of this design-in guide. The module has very specific power-on sequence requirements in order to power-up and operate correctly. Power sequencing the multiple voltage rails, as described in this section, is CRITICAL. If your design does not meet these requirements, the module will not boot.

#### Provide a system-level reset

Buffer and use the system reset signal RST# (J1 B56), described in Reset Signals, page 23, to reset all devices on the carrier board. The embedded controller controls the de-assertion of this signal with appropriate timings relative to power being stable. Timing requirements for power stable to reset de-asserted and reset de-asserted to device available are critical.

#### □ Create a power budget

Create a power budget that takes into account the current requirement of the module, as specified in Power Supply, page 45, and of the devices that are used with the module. Design your power supply to handle the maximum current requirement.

#### Determine thermal management

Determine what type of thermal management is required for your design. Use your power budget and the information provided in Thermal Management, page 33 of this design-in guide to design a heat spreader, if necessary.

#### **Follow the module's mechanical requirements**

Follow the exact mechanical requirements given in Mechanical Design, page 31 for mounting holes placement, position of the board-to-board connectors, and stack height on your carrier board design.

#### Use advanced layout and high-speed routing techniques

Follow the design constraints and routing guidelines described in Carrier Board Design, page 35 of this design-in guide. Adhering to good design practices for high-speed PCB design is essential. You should have your schematic 95% complete, especially the high-speed signals and buses of the module, power sequencing, and system reset, before you start board layout. Meet with your Eurotech representative to review your schematic before you begin layout. After your layout is complete, meet again to review your complete design.

#### □ Have a strategy to debug your design

Review your strategy to bring-up and to debug your design. Ensure that you have included the necessary support in your design. The maintenance serial port is extremely important in bring-up of a new design. Eurotech highly recommends including an external connection to SMC\_UART\_RX (J1 B57) and SMC\_UART\_TX (J1 B106) on your carrier board.

#### Critical design review

Do an in-depth review of your finished design, including final schematic and board layout, to ensure that you have met all the requirements described in this checklist and throughout this design-in guide. Again, ask your Eurotech representative questions.

### Prototype Bring-up Stage

Eurotech provides assistance in bringing-up your prototype at your site or ours. We have several tools that can assist the process including "stand-alone" BIOS releases, BIOS modifications to meet specific platform or test requirements, and power monitoring applications for the module. The "stand-alone" BIOS sets up the internal functions of the module and basic I/O functions. It is not dependent on any specific carrier board, devices, or circuits. This BIOS provides "basic" level functionality and can be used as a tool in the bring-up or debug of your unique carrier board.

#### Begin with the basics

Begin by checking basic functionality such as power, reset, and clocks. Verify that the power sequencing is as it should be and that the voltage regulator outputs are at nominal levels. Check that the system reset signal is asserted and deasserted according to the power sequencing requirements. Ensure all clocks necessary for bring-up are running properly.

#### □ Start with minimal devices

Minimize the number of devices required for bring-up. Using Eurotech's "debug" set of firmware is a good start. This firmware can be used (on case-by-case) basis as a debug and bring-up tool for your specific design prototyping or in the debugging phases of your development. It disables all NON-Critical-to-BOOT functions to simplify the system functionality to base level. After you have verified this base level, enable each subsystem as needed. Adding one device at a time will help determine which subsystem, if any, is having problems.

#### □ Utilize the maintenance port

Utilize the maintenance port output to identify problems during bring-up. This port provides important debug information including BIOS POST codes and error messages that enable you to monitor the operation of the module.

#### Use your Catalyst LP Development Kit

Use your Catalyst LP Development Kit to isolate problems. If a problem occurs during bring-up of your carrier board, try to duplicate the problem on the development kit.

#### Prototype bring-up review

Review your bring-up process and share lessons learned with your Eurotech representative.

### Acceptance of Customizations

Eurotech is committed to your design success. Using our support services throughout the development cycle ensures a complete and robust solution with which to move forward.

#### Customization Acceptance

Meet with your Eurotech representative to discuss acceptance of any customizations and to plan the steps toward production of your Catalyst LP design.

## **Development Kit**

The Catalyst LP Development Kit is designed to get the developer up and running quickly. The development kit includes the Catalyst LP, a standard development kit carrier board, and supporting peripheral devices. To provide flexibility and allow development across a broad spectrum of end-use applications, the carrier board maximizes the Catalyst LP functionality and implements many industry-standard interfaces. This configuration allows you to become familiar with the Catalyst LP functionality prior to customization for your specific application. In addition, the standard development kit carrier board provides a reference for custom carrier board design.

For a complete description of the Catalyst LP Development Kit, refer to the Catalyst LP Development *Kit User Manual (Eurotech document 110125-4000)*.

## **Related Documents**

This guide provides details about the various features of the Catalyst LP and about how it creates a system that meets your application needs. It extends the information provided in the *Catalyst LP Development Kit User Manual* and is intended for hardware design engineers. Design details are provided as guidelines for custom carrier board design.

The following documents are also important resources for the Catalyst LP.

| Document                                                   |             |

|------------------------------------------------------------|-------------|

| Catalyst XL - Catalyst LP Compatibility Technical Bulletin | 110125-1001 |

| Catalyst LP Development Kit User Manual                    | 110125-4000 |

| Catalyst LP Development Kit Quick Start                    | 110125-4001 |

| Catalyst Module Display Adapter User Manual                | 110122-4000 |

| Catalyst Module Installation and Removal                   | 110122-2014 |

| Catalyst System Management Programmer Reference            | 110122-2021 |

| Catalyst SMBus Programmer Reference                        | 110122-2022 |

| Catalyst I2C Bus Programmer Reference                      | 110122-2023 |

Table 1. Related Documents

Check the Eurotech support site (<u>http://support.eurotech-inc.com/</u>) for errata reports and for the latest releases of these documents.

# **Software Specifications**

Eurotech provides an application-ready platform including BIOS, operating system, and development environment. This section gives a brief description of the software support available for the Catalyst LP. For additional details, contact your local Eurotech representative.

## **Operating System Support**

The Catalyst LP is compatible with the following operating systems:

- Windows<sup>®</sup> Embedded Standard

- Wind River Linux 3.0 (future option)

- Select real-time operating systems

For details about available support of each operating system, contact your local Eurotech representative.

## BIOS

The Catalyst LP incorporates a custom system BIOS developed by Eurotech.

## **Software Development Kit**

Eurotech has developed a Software Development Kit (SDK) and its Application Programming Interface (API) for the following functions:

- System Management

- SMBus

- I<sup>2</sup>C bus

For details about the availability of these SDKs, contact your local Eurotech representative.

# Everyware<sup>™</sup> Software Framework

Everyware Software Framework (ESF) is an inclusive software framework that puts a middleware layer between the operating system and the OEM application. It provides industry-standard interfaces that shorten development time, simplify coding, and allow software to be ported from one Eurotech hardware platform to another. ESF is a future option for the Catalyst LP. If your application requires ESF, contact your local Eurotech representative.

Information about ESF is available at <u>http://esf.eurotech.com</u>.

# **Hardware Specifications**

## **Core Processor**

The Catalyst LP bases its architecture on an integrated two-chip solution comprised of the Intel Atom processor and Intel ICH8M. In addition, the Catalyst LP fully integrates system functions that include system management and control implemented by an advanced chip level solution, tightly integrated power management controls, system BIOS firmware memory, and optional Trusted Platform Management (TPM) for industry-standard secure data encryption. This fully integrated and flexible feature set increases product readiness and compliance. The following sections describe the functionality and feature set of this processor technology as it relates to the Catalyst LP architecture.

### Intel Atom Processor

At the core of the Catalyst LP is the Intel Atom processor N450 (single core) or the Intel Atom processor D510 (dual core). This high-performance architecture offers dual or single core processing with hardware-accelerated 2D/3D graphics display and video processing capabilities.

#### **External Interrupts**

The Catalyst LP provides several sources for external interrupts capable of generating a processor interrupt when the system is in power state S0. The following table lists these interrupt signals.

| Signal     | J1 Pin   | Description              |

|------------|----------|--------------------------|

| GPIO1      | A108     | Embedded controller GPIO |

| GPIO2      | A3       | Embedded controller GPIO |

| SMB_ALERT# | A33      | SMBus activity alert     |

|            | Table 2. | External Interrupts      |

For additional information about these signals, see General-Purpose Input and Output, page 23 and System Management Bus, page 20.

### Intel I/O Controller Hub

The Intel Atom processor operates in conjunction with the Intel ICH8M. This companion device provides a wide range of capabilities that include PCIe, USB, SATA, Intel HD Audio support, IDE/PATA, SMBus, LPC bus, Ethernet, and a RTC function. Subsequent sections describe each capability.

## Embedded Controller

An embedded controller included on the Catalyst LP performs two main functions: ACPI power management and hardware monitoring. It connects to the Intel ICH8M using the LPC bus.

Combined with the ICH8M and on-module power switch, the embedded controller supports ACPI power management. It functions, in conjunction with these devices, to control proper sequencing of voltages ensuring proper start-up, shutdown, and power saving transitions. For further details about power management, see Power Supply Architecture, page 25.

As a second function, the embedded controller provides hardware monitoring for voltage and temperature. Voltage monitoring measures the input power and on-module voltage regulators. Temperature monitoring measures temperatures on the Intel Atom processor die and near the memory chips. You can also monitor temperatures on your carrier board by connecting an external temperature sensor to the embedded controller  $I^2C$  bus provided on connector J1. For further details about the  $I^2C$  bus, see  $I^2C$  Bus, page 20.

In addition to the two main functions, the embedded controller performs extended functionality that includes optional battery management, device initialization, GPIO functions, wake event control, and customization for private SPI bus. For further details about the embedded controller's extended functionality, contact your local Eurotech representative.

## Trusted Platform Management (option)

The optional on-module TPM function is compliant with the Trusted Computer Group specification version 1.2. This function provides public key generation, public key storage encryption/decryption, storage of hashes, key endorsement, and TPM initialization. As an option, the TPM is included on the LPC bus.

## Memory

The Catalyst LP combined with a carrier board provides a variety of storage capabilities. The following sections describe the different types of memory supported and provide details about implementation.

## Synchronous DRAM

Double Data Rate Synchronous DRAM (DDR-2) is used on the Catalyst LP for system main memory and frame buffer memory. Options up to 2 GB are available. The Intel Atom processor supports unified memory architecture in which the integrated 2D/3D graphics controller memory is "unified" with the system main memory. The default frame buffer is 4 MB with options in the BIOS Setup for selecting an 8 MB option. Extended graphics memory space is available up to 256 MB. The graphics driver controls this size based on usage.

### Non-Volatile Memory

The Catalyst LP includes non-volatile memory for system BIOS storage and a real-time clock (RTC) functionality.

#### **BIOS and Configuration Data**

A serial interface flash memory device stores the BIOS boot firmware, BIOS Setup settings, and module configuration data on the Catalyst LP. Standard configuration is 2 MB. The flash device connects to the Intel ICH8M using a serial peripheral interface (SPI). This system BIOS memory supports pre-programmability at the device level, in-circuit programming on module, and updates using a run-time flash utility. In addition, programmable write protection is available using multiple flash sectors.

### **Real-Time Clock**

The Intel ICH8M includes a RTC function. It retains the system date and time when the system is powered down as long as the 3.3 V "always" power or backup power is provided to the chip. For further details, see Real-Time Clock, page 50.

## Flash SSD (option)

The Catalyst LP supports an optional on-module eMMC flash SSD. An 8 GB option is available in the standard module configuration. Options of 16 GB and 32 GB are available as custom module configurations. In addition to providing mass storage, this memory is a system boot option.

#### Notes:

The eMMC flash SSD option and PCIe slot 3 are mutually exclusive. If the flash SSD is populated, PCIe slot 3 is no longer available on connector J1. This option is set at time of production.

## External Memory Interfaces

Five types of external memory interfaces provide mass storage options on a carrier board. The Catalyst LP supplies the signals for an IDE/PATA interface, two SATA ports, nine USB ports, an SD/MMC interface, and up to four PCIe slots that can connect external memory to the module. Connector J1 provides the signals for each option. Include support circuitry and connectors on your carrier board.

The high-speed differential and single-ended signals associated with these external memory interfaces require strict routing constraints on the carrier board. For routing guidelines, see Design Guidelines, page 35.

#### **IDE/PATA Disk Drive**

The Catalyst LP provides an IDE/Parallel ATA (PATA) interface for mass storage supporting up to two devices: one master and one slave. A common application is to connect this interface to a 2.5-inch IDE/PATA disk drive.

| IDE/PATA Standard                              | Transfer Modes Supported                                                    | Transfer Rate (Mbps)                  |

|------------------------------------------------|-----------------------------------------------------------------------------|---------------------------------------|

| ATA-1<br>(ATA, IDE)                            | PIO modes 0, 1, 2<br>Single-word DMA modes 0, 1, 2<br>Multi-word DMA mode 0 | 3.3, 5.2, 8.3<br>2.1, 4.2, 8.3<br>4.2 |

| ATA-2, ATA-3<br>(EIDE, Fast ATA)               | PIO modes 3, 4<br>Multi-word DMA modes 1, 2                                 | 11.1, 16.6<br>13.3, 16.6              |

| ATA/ATAPI-4<br>(Ultra DMA, Ultra ATA)          | Ultra DMA modes 0, 1, 2<br>(a.k.a. Ultra DMA/33)                            | 16.7, 25.0, 33.3                      |

| ATA/ATAPI-5<br>(Ultra-DMA, Ultra ATA)          | Ultra DMA modes 3, 4<br>(a.k.a. Ultra DMA/66)                               | 44.4, 66.7                            |

| ATA/ATAPI-6<br>(Ultra-DMA, Ultra ATA)          | Ultra-DMA mode 5<br>(a.k.a. Ultra DMA/100)                                  | 100 (reads),<br>89 (writes)           |

| Table 3 Supported IDE/PATA Standards and Modes |                                                                             |                                       |

The following table lists supported IDE/PATA Standards and Modes.

Table 3. Supported IDE/PATA Standards and Modes

See the following section for limitations of the IDE/PATA and SATA interfaces.

#### **SATA Disk Drive**

The Catalyst LP supports two serial ATA (SATA) buses providing the option for high-capacity, removable storage SATA disk drives. These interfaces support the Serial ATA Specification, Revision 2.5 with data transfer rates of up to 3.0 Gbps.

Notes: Revision A modules support up to two SATA ports. SATA 2 and the IDE/PATA interface are mutually exclusive. If IDE/PATA is used, only SATA 1 is available.

Revision B modules support SATA 1, SATA 2, and IDE/PATA.

#### **USB Mass Storage Device**

A USB mass storage device can connect to one of nine USB ports on the Catalyst LP. Any USB device that has USB drivers installed on the Catalyst LP can connect to the USB host ports. For a description of these ports, see USB, page 19.

#### **SD** Cards

The Catalyst LP includes one Secure Digital and MultiMediaCard (SD/MMC) interface for memory and I/O expansion. You can use this interface to implement a SD/MMC socket on a carrier board providing mass storage or to develop custom unique add-in cards.

This SD/MMC interface is compliant with the following specifications:

- SD Spec. Part 1 Physical Layer Spec. Version 3.00

- SD Spec. Part A2 SD Host Controller Standard Spec. Version 2.00

- Compliant with SD Spec. Part E1 SDIO Spec. Version 2.00

- Compliant with SD Spec. Part 2 File System Spec. Version 2.00

- Compliant with MultiMediaCard System Spec. Version 4.2

In addition to the SD/MMC signals, connector J1 includes signals to control SD/MMC support circuitry on the carrier board. The interface includes signals to control a power FET and to drive a LED. For routing guidelines, see Design Guidelines, page 35.

#### **PCIe Memory Card**

A PCIe x1 memory card can connect to one of four PCIe x1 slots available on the Catalyst LP. For a description of the PCI Express capability, see PCI Express, page 18.

## Communications

The Catalyst LP supports several industry-standard channels for communication with peripheral and peer devices on the carrier board. These include PCI Express, USB, Gigabit Ethernet, I<sup>2</sup>C bus, and SMBus. The Catalyst LP does not limit flexibility by integrating fixed function I/O components. All communication signals are available on connector J1 providing flexibility and ease of implementation on the carrier board. This allows development of a unique carrier board optimized for your requirements.

#### PCI Express

A key capability of the Catalyst LP is its PCI Express (PCIe) support. In the standard configuration, the Intel ICH8M provides up to four PCIe one lane (PCIe x1) slots on connector J1. As a custom configuration, these PCIe slots can be configured as one PCIe four lane (PCIe x4) slot. Each slot is compliant with the PCI Express Base Specification, Revision 1.1 supporting 2.5 Gbps bandwidth in each direction. These high-speed differential pairs require strict routing constraints on the carrier board and AC coupling. For routing guidelines, see Design Guidelines, page 35.

Notes:

The eMMC flash SSD option and PCIe slot 3 are mutually exclusive. If the flash SSD is populated, PCIe slot 3 is no longer available on connector J1. This option is set at time of production.

| Connector J1<br>Pin  | Connector J1<br>Signal Name                                          | Intel ICH8M<br>PCIe Port |

|----------------------|----------------------------------------------------------------------|--------------------------|

| A99, A98<br>B95, B94 | PCIE_TXP2_SLOT0, PCIE_TXN2_SLOT0<br>PCIE_RXP2_SLOT0, PCIE_RXN2_SLOT0 | 1                        |

| B99, B98<br>A95, A94 | PCIE_TXP2_SLOT1, PCIE_TXN2_SLOT1<br>PCIE_RXP2_SLOT1, PCIE_RXN2_SLOT1 | 2                        |

| A84, A85<br>A87, A88 | PCIE_TXP2_SLOT2, PCIE_TXN2_SLOT2<br>PCIE_RXP2_SLOT2, PCIE_RXN2_SLOT2 | 3                        |

| B16, B17<br>B18, B19 | PCIE_TXP2_SLOT3, PCIE_TXN2_SLOT3<br>PCIE_RXP2_SLOT3, PCIE_RXN2_SLOT3 | 4                        |

The following table shows the mapping of connector J1 to the Intel ICH8M's PCIe ports.

Table 4. PCIe Slot Mapping

An on-module clock generator supplies the PCIe clocks for two of the four ports: PCIe slot 0 and PCIe slot 1. To provide a reference clock for PCIe slot 2 and PCIe slot 3, include a differential buffer on your carrier board. Buffer the reference clock for PCIe slot 0 or PCIe slot 1 to drive multiple clocks. Use a buffer similar to the type of IDT ICS9DBL411.

Additional input signals to the module, CLK\_SLOT0\_OE# and CLK\_SLOT1\_OE#, control each reference clock. On a carrier board, these signals connect to the PCIe sockets indicating the presence of a PCIe device. When activated, this signal enables the PCIe clock for the device. For electrical specifications, see PCIe Clock Generator, page 47.

### USB

The Intel ICH8M provides nine Universal Serial Bus (USB) ports. All ports function as general-purpose USB host ports supporting the USB 1.1 specification operating at low (1.5 Mbps) and full (12 Mbps) speeds and the USB 2.0 specification operating at high speed (480 Mbps).

The following table describes the USB connectivity on the Catalyst LP.

| Connector J1<br>Pin | Connector J1<br>Signal Name | Intel ICH8M<br>USB Port |

|---------------------|-----------------------------|-------------------------|

| A71, A72            | USB_PP0, USB_PN0            | 0                       |

| B71, B72            | USB_PP1, USB_PN1            | 1                       |

| A68, A69            | USB_PP2, USB_PN2            | 2                       |

| B67, B68            | USB_PP3, USB_PN3            | 3                       |

| A65, A66            | USB_PP4, USB_PN4            | 4                       |

| B64, B65            | USB_PP5, USB_PN5            | 5                       |

| A62, A63            | USB_PP6, USB_PN6            | 6                       |

| B61, B62            | USB_PP7, USB_PN7            | 7                       |

| B74, B75            | USB_PP8, USB_PN8            | 9                       |

Table 5. USB Port Connectivity

USB0-5 also include over-current detection inputs. Use these USB host ports to connect to devices external to the carrier board. USB mouse and keyboard are the most common client devices, but you can connect any USB device that has USB drivers installed on the Catalyst LP. USB6, USB7, and USB8 do not include the associated over-current detection signals. When possible, connect these ports to devices on the carrier board. For electrical specifications, see USB, page 47.

In order to create a fully functioning USB host port, include the host power supply, current limiter circuits, EMI chokes, and over-voltage protection on your carrier board. The USB protocol allows client devices to negotiate the power they need from 100 mA to 500 mA in 100 mA increments. The carrier board must supply the 5 V power required by client devices. Use a power switch with the corresponding over-current detection for each port. For routing guidelines, see Design Guidelines, page 35.

## Gigabit Ethernet

The Intel ICH8M includes a Gigabit Ethernet Controller that conforms to the IEEE 802.3 standard. This device connects to an Intel<sup>®</sup> 82567 Gigabit Ethernet Physical Layer Transceiver located on the module, supporting a Media Dependent Interface (MDI) for 10Base-T, 100Base-TX, and 1000Base-T applications. For information about this device, refer to <u>www.intel.com</u>. In addition, the transceiver drives three programmable LED control signals which are available on connector J1.

Depending on your application, this MDI interface may be used directly or magnetics and an RJ-socket may be required on your carrier board to complete the connection to your network. Contact your local Eurotech representative for additional information about the magnetics recommended for use on the carrier board. For routing guidelines, see Design Guidelines, page 35.

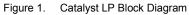

## Carrier I<sup>2</sup>C Bus

$I^2C$  (Inter-IC) bus is a multi-master, "two-wire" synchronous serial bus for communications between integrated circuits (ICs) and for addressing peripherals in a system. The Catalyst LP provides an external connection to its  $I^2C$  bus with the embedded controller acting as the bus master.

The following diagram illustrates the I<sup>2</sup>C architecture on the Catalyst LP.

Figure 2. I<sup>2</sup>C Bus Architecture

When possible, use the SMBus to communicate with devices on the carrier board instead of the carrier  $I^2C$  bus. When this bus is used on your carrier board, power all devices connected to it using the 3.3 V "Always" power (V3.3A) or isolate the devices from the bus when powered off. Notice that the module does not include termination on the  $I^2C$  bus. Include  $10k\Omega$  pull-up resistors to V3.3A on the carrier board. For electrical specifications, see Carrier  $I^2C$  Bus, page 47.

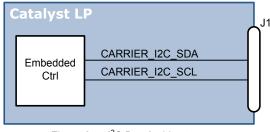

### System Management Bus

System Management Bus (SMBus) follows the same operating principles as  $I^2C$ . Similar to  $I^2C$ , SMBus is a "two-wire" interface allowing multiple devices to communicate with each other. Devices function as bus masters and bus slaves. SMBus enables communication between devices and allows connection of devices that require legacy software accessibility thru standard SMB addressing.

The Catalyst LP provides an external connection on connector J1 to its SMBus with the Intel ICH8M acting as bus master. This bus supports the SMBus 2.0 Specification. In addition, the module supports hardware alerting on the SMBus using the I/O signal SMB\_ALERT#.

Notes:

SMBus is not compatible with all I<sup>2</sup>C devices. Review the device data sheet carefully before connecting an I<sup>2</sup>C device to the SMBus.

The following diagram illustrates the SMBus architecture.

Figure 3. SMBus Architecture

Notice that the module includes pull-up resistors to V3.3A on the SMBus. On your carrier board, power all devices connected to this bus using the V3.3A power or isolate the devices from the bus when powered off. For electrical specifications, see SMBus, page 47.

The following table lists the addresses of the SMBus devices on the Catalyst LP.

| Module Device | Address   | Function |

|---------------|-----------|----------|

| Reserved      | 1101 0010 | Write    |

|               | 1101 0011 | Read     |

Table 6. SMBus Addresses

## Display and User Interface

The Intel Atom processor includes an integrated 2D/3D graphics engine supporting hardwareaccelerated graphics display and video processing capabilities. The processor provides two independent display outputs. A LVDS output drives the primary display, while a VGA output drives a secondary display. In addition, the processor provides discrete backlight control signals.

This section summarizes the Catalyst LP graphics display and video processing capabilities. Display resolutions are specified at the maximum refresh rate and color depth. Higher resolutions may be possible at lower refresh rates and color depths. This relationship is due primarily to the increased processing bandwidth required at higher output resolutions.

## LVDS Display and Backlight Control

The growing demand for higher resolution displays has been meet with design limitations on the interface between the LCD and graphics controller. Increased resolution LCDs require an increased clock speed, a larger number of data lines, and a higher power consumption. LVDS serial data transmission addresses these issues by providing a high-speed, low-power interface on a single pair of wires per channel. The Catalyst LP supplies a LVDS output to drive a primary display.

The following table summarizes the LVDS display output capabilities.

| Feature    | LVDS Display                       |  |  |

|------------|------------------------------------|--|--|

| Resolution | Up to 1366 x 768, 18-bit color     |  |  |

|            | Table 7. LVDS Display Capabilities |  |  |

The LVDS display output consists of three LVDS data pairs, as well as a LVDS pixel clock, supporting 18-bit color. If your application requires transmission over a display cable greater than 7 inches, include an LVDS buffer/repeater on your carrier board to boost the data and pixel clock signals. Use controlled impedance cables that target 97  $\Omega$ .  $\pm$  20%. Cables should not introduce major impedance discontinuities that cause signal reflections. The differential pairs also require strict routing constraints on the carrier board. For routing guidelines, see Design Guidelines, page 35.

Additional capabilities include the discrete signal L\_VDDEN (J1 pin A32) that controls power to the display and an I<sup>2</sup>C interface (L\_DDC\_DATA on J1 pin B28, L\_DDC\_CLK on J1 pin A29) for communication with the LCD Display Data Channel (DDC). For electrical specifications, see LVDS Display and Backlight, page 48.

## Backlight

Most LCDs include one or more cold-cathode fluorescent lamp (CCFL) tubes to backlight the displays. Backlight inverters drive the panel backlights. These circuits are typically external to the display and generate the several hundred volts required to drive the CCFL tubes. Backlights can easily become the greatest source of power consumption in a portable system. To reduce power consumption, most backlight inverters include control signals to dim and turn off the backlight. To support these features, the Catalyst LP supplies three backlight control signals and an I<sup>2</sup>C bus (L\_CTLB\_DATA on J1 pin B25, L\_CTLA\_CLK on J1 pin B29) for communication with the backlight. For electrical specifications, see LVDS Display and Backlight, page 48.

The following table describes the backlight control signals.

| Signal           | J1 Pin | Туре | Description                                          |

|------------------|--------|------|------------------------------------------------------|

| L_BKLTCTL        | B33    | 0    | Controls the intensity of the backlight              |

| L_BKLTEN         | B32    | 0    | Turns power to the backlight on or off               |

| L_BKLTSEL0_GPIO# | B58    | 0    | Selects backlight control (PWM vs. I <sup>2</sup> C) |

|                  |        |      |                                                      |

Table 8. Backlight Control Signals

## VGA Display

As a secondary display option, the Catalyst LP drives an analog RGB output. This output provides red, green, and blue data, as well as horizontal sync and vertical sync signals. To connect to a VGA display, add termination, output filters, and buffers on your carrier board. For routing guidelines, see Design Guidelines, page 35.

The following table summarizes the VGA display output capabilities.

| Feature         |      | VGA Display                         |  |  |

|-----------------|------|-------------------------------------|--|--|

| Resolution D510 |      | Up to 2048 x 1536 x 32 bpp at 60 Hz |  |  |

|                 | N450 | Up to 1400 x 1050 x 32 bpp at 60 Hz |  |  |

|                 |      |                                     |  |  |

Table 9. VGA Display Capabilities

In addition, the module provides a Display Data Channel (DDC) serial bus (VGA\_DDC\_SDA on J1 pin A30, VGA\_DDC\_CLK on J1 pin B30) for monitor Plug and Play capability with various computer displays. For electrical specifications, see VGA Display, page 48.

## **Inputs and Outputs**

Several signals on the Catalyst LP support I/O expansion and system management. The module includes a Low Pin Count bus supporting legacy I/O capabilities and multiple discrete I/O signals performing system reset, power control, and general-purpose input and output. Connector J1 includes all I/O signals.

## Low Pin Count Bus

In response to the transition from ISA-based systems, the Low Pin Count (LPC) bus provides a migration path for legacy I/O capabilities. This bus enables general-purpose I/O expansion and provides communication to low-bandwidth devices. For this purpose, the Intel ICH8M supplies a LPC bus supporting the supporting the Low Pin Count Interface Specification, Revision 1.1. On the Catalyst LP, the LPC bus connects to the Intel ICH8M, the embedded controller, and an optional TPM.

The following diagram illustrates the LPC bus architecture.

Note:

For details about the termination on individual signals on the LPC bus, see J1, page 40. Figure 4. LPC Bus Architecture Externally, the LPC bus provides general-purpose expansion. A common application on the carrier board includes a Super I/O Controller that provides I/O capabilities such as serial ports, keyboard, mouse, IrDA, and general-purpose I/O. Ensure that the LPC signals are routed as critical nets on your carrier board and include  $10k\Omega$  pull-up resistors to V3.3S on the LPC\_ADx signals. For routing guidelines, see Design Guidelines, page 35.

## **Reset Signals**

One of two signals resets the circuitry on the module and carrier board. One signal originates from the module, while the second signal originates from the carrier board. The output signal RST# includes several loads on the Catalyst LP. Include a buffer on the carrier board to drive additional loads.

The following table compares the reset signals.

| 0                                                                                                                  | Use as a power-on reset to reset all devices on the carrier board.<br>Output is driven by the module, forces complete system hardware<br>reset, and is used for proper reset timing and logic synchronization. |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                                                                                                                    |                                                                                                                                                                                                                |  |  |  |  |

| FP_RESET#         A59         I         Do not use this signal as a power-on detected until RST# is de-asserted.   |                                                                                                                                                                                                                |  |  |  |  |

| Input initiates a hardware reset including the Intel Atom processor and<br>Intel ICH8M.<br>Table 10. Reset Signals |                                                                                                                                                                                                                |  |  |  |  |

In addition to the hardware resets, the input signal H INIT# (J1 pin B3) initiates a soft reset of the

module. For electrical specifications, see Reset Signals, page 46.

## General-Purpose Input and Output

The Catalyst LP provides four general-purpose input and output (GPIO) signals, as described in the following table. For electrical specifications, see General-purpose Inputs and Outputs, page 49.

| Signal                      | J1 Pin | Description              |  |  |  |

|-----------------------------|--------|--------------------------|--|--|--|

| GPIO1                       | A108   | Embedded controller GPIO |  |  |  |

| GPIO2                       | A3     | Embedded controller GPIO |  |  |  |

| GPIO3                       | A2     | Intel ICH8M GPIO1        |  |  |  |

| GPIO4 B53 Intel ICH8M GPIO8 |        |                          |  |  |  |

|                             |        |                          |  |  |  |

Table 11. GPIO Signals

GPIO1 and GPIO2 are software-controlled using the Catalyst System Management API. For details about this API, refer to the *Catalyst System Management Programmer Reference (Eurotech document #110122-2021)*. Future revisions of the API will support the Intel ICH8M GPIO.

## **Intel High Definition Audio**

The Intel High Definition Audio (Intel HD Audio) Specification implements high quality audio in a PC environment. The specification defines a uniform interface between a host computer and audio codec specifying register control, physical connectivity, programming model, and codec architectural components. The Intel ICH8M provides an Intel HD Audio interface capable of supporting up to two external audio codecs. Docking functionality is supported allowing control of an external switch for isolation of the codec within a docking station during normal docking request and acknowledge cycles.

All Intel HD Audio signals are available on connector J1. The Catalyst LP supports only 3.3 V signalling levels. For electrical specifications, see Intel High Definition Audio, page 49. Include audio codecs along with amplifiers, switches, and connectors on your carrier board. For routing guidelines, see Design Guidelines, page 35.

## **Power Requirements**

Power management is especially critical in high-performance systems that also require low power dissipation. Handheld and portable systems available today never really turn "off". They make use of power management techniques that cycle the electronics into power saving modes, but never fully remove power from the full system.

Embedded system designers using the Catalyst LP should have a clear understanding of how the system design allocates power usage. Create a power budget that takes into account the types of devices that are used with the Catalyst LP. For baseline power consumption for the module, see Power Consumption, page 46. This section provides information about power and power management on the Catalyst LP.

### Low Power States

The Catalyst LP supports the Advanced Configuration and Power Interface (ACPI), version 2.0. Unlike previous power standards that were BIOS-based, ACPI allows OS-directed power management. It specifies an industry-standard interface for both hardware and software that facilitates power and thermal management. This section describes how the Catalyst LP makes use of the ACPI low power modes.

The ACPI specification defines the low power states for ACPI-compliant systems. The following table describes the states supported by the Catalyst LP.

| State      | Mode             | Description                                                                                                                                                                                                                                                                                                            |

|------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| S0         | Full Operation   | All devices are operational with dynamic power management functions active.                                                                                                                                                                                                                                            |

| <b>S</b> 3 | Standby or Sleep | The Intel Atom processor and Intel ICH8M are powered<br>down. Active operating system context stored in DRAM is<br>retained using low-power self-refresh. Wake events are<br>active and enable a transition back to full operation.                                                                                    |

| S4         | Hibernation      | The Intel Atom processor, Intel ICH8M, and DRAM are<br>powered down. Operating system context is saved to disk<br>storage prior to powering down system voltage rails. Limited<br>wake events are active. Resume to full operation is<br>dependent on numerous system components including the<br>disk storage device. |

| S5         | Power down       | The Intel Atom processor, Intel ICH8M, and DRAM are<br>powered down. The embedded controller is active but may<br>be in low-power mode. No operating system context is<br>preserved.                                                                                                                                   |

Table 12. ACPI Power States

Wake events transition the Catalyst LP from a low-power state back to full operation. The following table lists the signals that can function as wake events. These signals are valid as wake event inputs in power state S3.

| Wake Event                                                | J1 Pin | ICH8M Pin | Description          |  |

|-----------------------------------------------------------|--------|-----------|----------------------|--|

| GPIO4                                                     | B53    | AE16      | Intel ICH8M GPIO8    |  |

| GPIO3 A2 AJ8 Intel ICH8M GPIO1                            |        |           |                      |  |

| SMB_ALERT#                                                | A33    | AG22      | SMBus activity alert |  |

| PCIE_WAKE# B55 AE17 Standard I/O device wake event signal |        |           |                      |  |

| BTN_ONOFF#                                                | B59    | -         | Power button input   |  |

|                                                           |        |           |                      |  |

Table 13. Wake Events

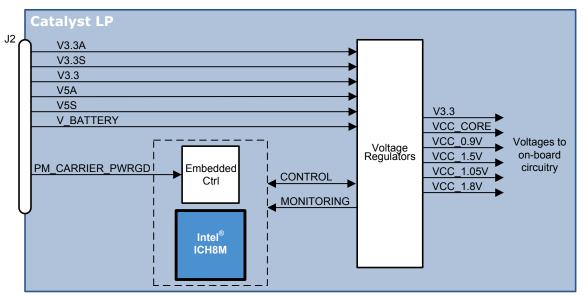

## **Power Supply Architecture**

The architecture of the power supply partitions the power generation across the Catalyst LP and the carrier board. The module requires 5 V and 3.3 V input voltages supplied by the carrier board. It is the responsibility of the carrier board designers to provide input power protection as required by their application. This is especially important if the power supply wires will be subject to EMI/RFI or ESD. On-module regulators generate the core power and all other powers required by the supporting circuitry. For electrical specifications and details about each power rail, see Power Supply, page 45.

#### Input Power Voltages

The following table describes the input power voltages required by the Catalyst LP.

| Name      | Power State                                               | Description                                                                 |

|-----------|-----------------------------------------------------------|-----------------------------------------------------------------------------|

| V3.3A     | S4 exit,<br>S5 exit,<br>S0 operation,<br>and S3 operation | 3.3 V "always" power for up/down circuitry only                             |

| V3.3S     | S0 operation                                              | 3.3 V normal operating power                                                |

| V3.3      | S0 operation<br>and S3 operation                          | 3.3 V primary supply voltage for most of the<br>on-board regulated voltages |

| V5A       | S4 exit,<br>S5 exit,<br>S0 operation,<br>and S3 operation | 5 V "always" power for up/down circuitry only                               |

| V5S       | S0 operation                                              | 5 V normal operating power                                                  |

| V_BATTERY |                                                           | Backup power for the RTC                                                    |

Table 14.Input Power Voltages

Each power rail should be routed as a power plane on your carrier board with sufficient bulk decoupling and local decoupling on each plane. For additional details about carrier board design, see Design Guidelines, page 35.

#### Notes:

The V5A rail should lead the V3.3A rail during ramp up.

The V5S rail should lead the V3.3S rail during ramp up or not lag by more than 0.7 V. It is acceptable for these two voltage rails to ramp up at the same time.

For an example circuit, see the Eurotech reference carrier board schematic.

**EUROTECH**

The following diagram illustrates the layout of the Catalyst LP power supply.

Figure 5. Power Supply Architecture

In addition to the input power voltages, connector J2, page 44 includes the signal PM\_CARRIER\_PWRGD. This input from the carrier board indicates that all input power voltages are fully operational and within tolerance.

**Notes:** The carrier board must provide the PM\_CARRIER\_PWRGD signal to represent the readiness for operation.

The embedded controller functions, in conjunction with the Intel ICH8M and on-module power switch, to control proper sequencing of voltages allowing for proper start-up, shutdown, and power saving transitions. In addition, it monitors input power voltages and the on-module voltage regulators. For additional details about the embedded controller, see Embedded Controller, page 15.

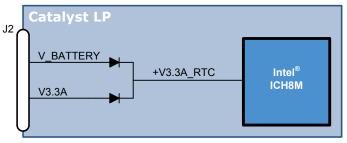

#### **RTC Backup Power**

The Catalyst LP includes a RTC function that retains the system date and time when the system is powered down as long as the 3.3 V "always" power or backup power is provided to the module. Including a long-life 3 V battery on a carrier board is a common method to supply backup power. Use series elements, such as a diode and resistor, on the V\_BATTERY output from your carrier board based on your specific requirements.

On the Catalyst LP, the V\_BATTERY power input has a diode-OR with V3.3A, as shown in the following diagram.

Figure 6. RTC Backup Power Architecture

For specifications, see Power Supply, page 45 and Real-Time Clock, page 50.

#### **Power Switch**

The input signal BTN\_ONOFF# (J1 pin B59) controls a power switch included on the Catalyst LP. The function of the BTN\_ONOFF# signal is dependent on the embedded controller/BIOS setup and the configuration of the operating system. The response of the system can be managed by this combination. On the standard development kit, this input is connected to a momentary button on the carrier board. Pressing this external momentary button turns the power on and off. For electrical specifications, see Power Supply, page 45.

The following table details the operation of the BTN\_ONOFF#.

| BTN_ONOFF#                                    | Operation                                                                                                                                                                                                                                                                                                                  |

|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Momentary assertion<br>(less than 4 seconds)  | On standard development kit:<br>From shutdown, initiates a power-up sequence to full operation.<br>From full operation, initiates an orderly shutdown sequence and turns off power.<br>Options based on system configuration:<br>From full operation, enters system sleep state.<br>From sleep, returns to full operation. |

| Continuous assertion (greater than 4 seconds) | Initiates a "4 second over-ride" and turns off power without notification to the<br>operating system.                                                                                                                                                                                                                      |

|                                               |                                                                                                                                                                                                                                                                                                                            |

Notes:

Once the V5A and V3.3A rails are applied, the  ${\tt BTN\_ONOFF\#}$  signal is not detected for 400 msec.

### **Power State Signals**

The Catalyst LP provides three control signals on connector J1 indicating the power state. The Intel ICH8M controls the two power state signals, PM\_EN\_S0# (J1 pin B104) and PM\_EN\_S3# (J1 pin B107). The on-module power switch controls the remaining signal, PM\_EN\_PWR (J1 pin B105). For electrical specifications, see Power Supply, page 45.

The following table lists these signals with the power states and input power voltages active in each state.

| State | Active power rails         | PM_EN_PWR | PM_EN_S3# | PM_EN_S0# |

|-------|----------------------------|-----------|-----------|-----------|

| S0    | V3.3, V5S V3.3S V5A, V3.3A | High      | Low       | Low       |

| S3    | V3.3, V5A, V3.3A           | High      | Low       | High      |

| S4    | V5A, V3.3A                 | Low       | High      | High      |

| S5    | V5A, V3.3A                 | Low       | High      | High      |

Table 16. Low Power States

#### Notes:

Implement the exact power supply sequencing as described in this section. The module has very specific power-on sequence requirements in order to power-up and operate correctly. Power sequencing the multiple voltage rails is CRITICAL. If your design does not meet these requirements, the module will not boot.

For additional details about best practices for power sequencing, contact your local Eurotech representative.

The following timing diagrams describe the relationship of the power state control signals on the Catalyst LP.

#### Power-on initiated by power button press

In a typical system power on, the falling edge of BTN\_ONOFF# drives PM\_EN\_PWR high. A hardware latch on the Catalyst LP controls PM\_EN\_PWR. The embedded controller monitors BTN\_ONOFF# until the rising edge of BTN\_ONOFF#.

After sampling BTN\_ONOFF# high, the embedded controller waits for PM\_CARRIER\_PWRGD to be asserted high before driving PM\_EN\_S3# active (logic level low). After PM\_CARRIER\_PWRGD is asserted, S3 power rails internal to the Catalyst LP are enabled with the assertion of PM\_EN\_S3# and powered by V3.3. After the S3 power rails are within specification on the module and on the carrier board, the ICH8M asserts PM\_EN\_S0# (logic level low). The time from PM\_EN\_S3# active to PM\_EN\_S0# active depends on how quickly the carrier supplies V3.3.

(This diagram will be provided in future revisions.)

Figure 7. Power-on initiated by power button press

#### Standby (Enter S3)

The following diagram shows the Catalyst LP transitioning from S0 to S3. This transition can be initiated by the operating system or the BTN\_ONOFF# input in combination with the operating system. The PM\_EN\_S0# signal will be de-asserted, and all S0 power rails on the Catalyst LP module will be turned off. The PM\_CARRIER\_PWRGD signal is not monitored for 10 ms following the de-assertion of PM\_EN\_S0#. This allows the carrier board S0 power rails to be turned off and PM\_CARRIER\_PWRGD to provide status of the power rails remaining on in S3.

| V3.3A, V5A  |                                              |                                                            |

|-------------|----------------------------------------------|------------------------------------------------------------|

| BTN_ONOFF#  | User or operating system initiates a Standby |                                                            |

| PM_EN_PWR   |                                              | PM_CARRIER_PWRGD is ignored<br>10 ms after a state change. |

| PM_CARRIER_ | PWRGD                                        | X                                                          |

| PM_EN_S3#   |                                              |                                                            |

| V3.3        |                                              |                                                            |

| PM_EN_S0#   |                                              |                                                            |

| V3.3S, V5S  |                                              |                                                            |

|             | Power State S0                               | Power State S3                                             |

|             | Figure 8. Standby (Enter S3)                 | :                                                          |

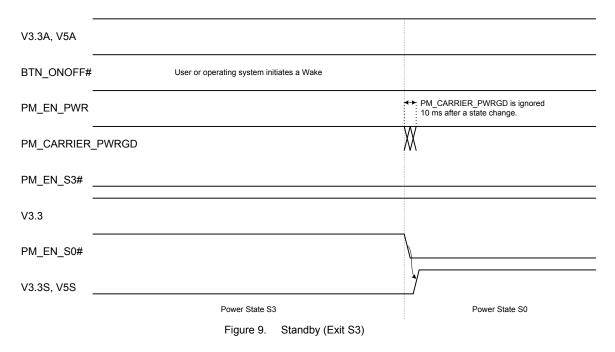

#### Standby (Exit S3)

The following diagram shows the system exiting S3. The system may wake from S3 because of any event shown in Table 13, page 24. PM\_EN\_S0# will be asserted causing all S0 power rails on the Catalyst LP to be turned on. PM\_CARRIER\_PWRGD will not be monitored for 10 ms after PM\_EN\_S0# is de-asserted. This provides time for all S0 power rails on the carrier board to be turned on and within specification.

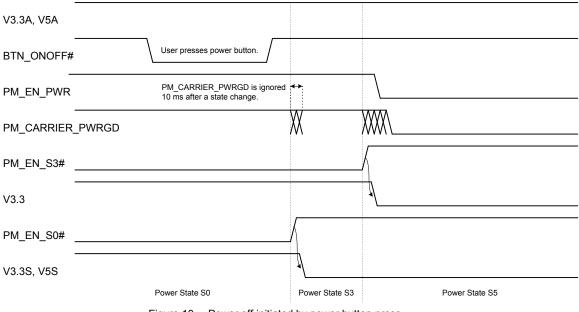

#### Power off initiated by power button press

The following diagram shows a system powering off because of an assertion of the BTN\_ONOFF# signal. Depending on operating system settings, a system may power off or sleep due to asserting BTN\_ONOFF#. If set for a power off, the operating system will save all information needed and the system will perform a graceful shutdown. PM\_EN\_S0# will be de-asserted, followed by PM\_EN\_S3# and PM\_EN\_PWR being de-asserted.

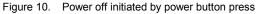

#### System shutdown initiated by operating system

The following diagram shows a system powering at the request of the operating system. The user could initiate this via software control. The operating system will save all information needed and teh system will perform a graceful shutdown. PM\_EN\_S0# will be de-asserted, followed by PM\_EN\_S3# and PM\_EN\_PWR being de-asserted.

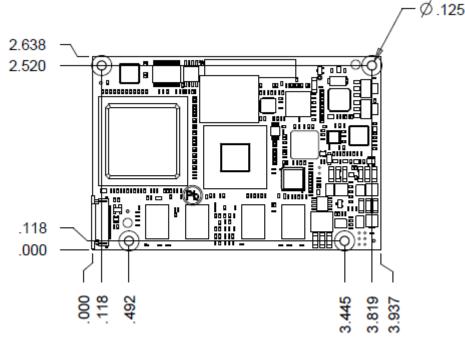

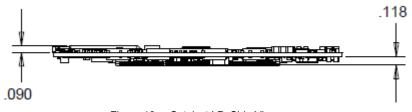

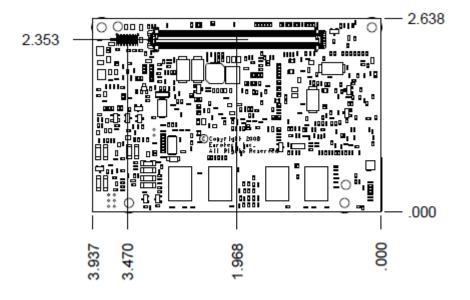

# **Mechanical Specifications**

This section describes mechanical and thermal design guidelines for the Catalyst LP.

## **Mechanical Design**

## Mechanical Drawing

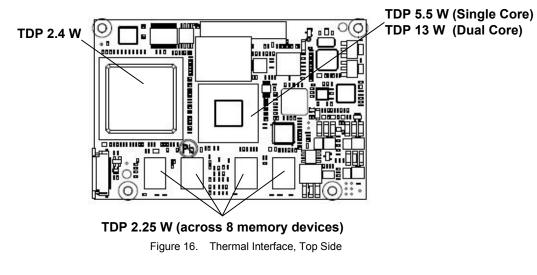

The following mechanical drawing specifies the dimensions of the Catalyst LP, as well as locations of key components on the board. All dimensions are in inches.

Figure 12. Catalyst LP, Top View

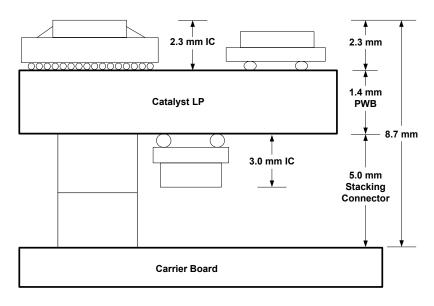

Figure 13. Catalyst LP, Side View