## **USER MANUAL**

CPU-301-16

Development Kit

Rev 1 – August 2013 – 110127-50001

## **Trademarks**

All trademarks both marked and not marked appearing in this document are the property of their respective owners.

# **Document Revision History**

| REVISION | DESCRIPTION     | DATE        |

|----------|-----------------|-------------|

| 1        | Initial release | August 2013 |

# **Table of Contents**

| Trademarks                                    | 2  |

|-----------------------------------------------|----|

| Document Revision History                     | 2  |

| Table of Contents                             | 3  |

| Important User Information                    | 5  |

| Safety Notices and Warnings                   |    |

| Life Support Policy                           |    |

| Warranty                                      |    |

| WEEE                                          |    |

|                                               | _  |

| RoHS                                          |    |

| Technical Assistance                          |    |

| Conventions                                   |    |

| Product Overview                              |    |

| Block Diagram                                 | 9  |

| Features                                      | 10 |

| Related Documents                             |    |

| Connectors, Switches, Jumpers, and Indicators | 12 |

| Identifying Connectors                        |    |

| Switches, Indicators, and Jumpers             |    |

| Boot Configuration                            |    |

| Carrier Board Switches                        |    |

| Carrier Board LED Indicators                  | 14 |

| Carrier Board Jumpers                         | 15 |

| Signal Headers                                |    |

| J1: Docking Connector                         |    |

| J2: Docking Connector                         |    |

| J3: USB Host 1<br>J4: USB Host 2              |    |

| J5: Gigabit Ethernet                          |    |

| J6: Line Out                                  |    |

| J7: Microphone                                |    |

| J8: Keypad                                    |    |

| J9: SATA                                      |    |

| J10: JTAG, CMOS Camera, and GPIO              | 18 |

| J11: JTAG (Option)                            |    |

| J13: Mini PCle (x1)                           |    |

| J15: Speaker                                  |    |

| J14: USB OTG<br>J19: CAN                      |    |

| J20: CAN                                      |    |

| J21: Serial A                                 |    |

| J22: Serial B                                 |    |

| J23: Serial C and Serial D                    |    |

| J27: DC Power Input                           | 21 |

| J28: Touch Panel (8-wire)                     | 21 |

| J29: LVDS Display 1                           |    |

| J31: microSD Card                             |    |

| J30: SD Card                                  |    |

| J32: LVDS Display 0<br>J37: USB Host 3        |    |

| 001. 00D H00t 0                               |    |

| J38: GPIO                                    | 23 |

|----------------------------------------------|----|

| J39: Digital Display                         | 24 |

| J40: Backlight 0                             | 24 |

| J41: Backlight 1                             |    |

| J43: SIM                                     |    |

| J44: CMOS Camera                             | 25 |

| J45: MIPI Camera                             | 26 |

| J46: Backlight 2                             | 26 |

| J47: MIPI Ďisplay                            |    |

| J48: USB Host 3 (Option)                     |    |

| J49: HDMI Display                            |    |

| J50: USB Host 1 (Alternate)                  | 28 |

| J51: USB Host 2 (Option)                     |    |

| System Specifications                        | 29 |

| Power Supply                                 | 29 |

| Electrical                                   | 29 |

| GPIO Header                                  |    |

| USB Host Ports                               |    |

| Audio Interface                              |    |

| General                                      | 30 |

| General-Purpose <sup>p</sup> C Bus Addresses | 30 |

| ·                                            |    |

| ·                                            | 31 |

| Appendix A – Reference Information           |    |

# **Important User Information**

In order to lower the risk of personal injury, electric shock, fire, or equipment damage, users must observe the following precautions as well as good technical judgment, whenever this product is installed or used.

All reasonable efforts have been made to ensure the accuracy of this document; however, Eurotech assumes no liability resulting from any error/omission in this document or from the use of the information contained herein.

Eurotech reserves the right to revise this document and to change its contents at any time without obligation to notify any person of such revision or changes.

## **Safety Notices and Warnings**

The following general safety precautions must be observed during all phases of operation, service, and repair of this equipment. Failure to comply with these precautions or with specific warnings elsewhere in this manual violates safety standards of design, manufacture, and intended use of the equipment. Eurotech assumes no liability for the customer's failure to comply with these requirements.

The safety precautions listed below represent warnings of certain dangers of which Eurotech is aware. You, as the user of the product, should follow these warnings and all other safety precautions necessary for the safe operation of the equipment in your operating environment.

#### Installation in Enclosures

In the event that the product is placed within an enclosure, together with other heat generating equipment, ensure proper ventilation.

### Do Not Operate in an Explosive Atmosphere

Do not operate the equipment in the presence of flammable gases or fumes. Operation of any electrical equipment in such an environment constitutes a definite safety hazard.

### Alerts that can be found throughout this manual

The following alerts are used within this manual and indicate potentially dangerous situations.

#### Danger, electrical shock hazard:

Information regarding potential electrical shock hazards:

- Personal injury or death could occur. Also damage to the system, connected peripheral devices, or software could occur if the warnings are not carefully followed.

- Appropriate safety precautions should always be used, these should meet the requirements set out for the environment that the equipment will be deployed in.

#### Warning:

Information regarding potential hazards:

Appropriate safety precautions should always be used, these should meet the requirements set out for the environment that the equipment will be deployed in.

#### Information and/or Notes:

These will highlight important features or instructions that should be observed.

## Use an Appropriate Power Supply

- Only start the product with a power supply that conforms to the voltage requirements as specified in Power Supply, page 29. In case of uncertainty about the required power supply, please contact your local Eurotech Technical Support Team.

- Avoid overcharging power-points.

#### Antistatic Precautions

To avoid damage caused by ESD (Electro Static Discharge), always use appropriate antistatic precautions when handing any electronic equipment.

## **Life Support Policy**

Eurotech products are not authorized for use as critical components in life support devices or systems without the express written approval of Eurotech.

## Warranty

For Warranty terms and conditions users should contact their local Eurotech Sales Office. See Eurotech Worldwide Presence, page 33 for full contact details.

## **WEEE**

The information below is issued in compliance with the regulations as set out in the 2002/96/EC directive, subsequently superseded by 2003/108/EC. It refers to electrical and electronic equipment and the waste management of such products. When disposing of a device, including all of its components, subassemblies, and materials that are an integral part of the product, you should consider the WEEE directive.

This device is marketed after August 13, 2005 and you must separate all of its components when possible and dispose of them in accordance with local waste disposal legislations.

- Because of the substances present in the equipment, improper use or disposal of the refuse can cause damage to human health and to the environment.

- With reference to WEEE, it is compulsory not to dispose of the equipment with normal urban refuse and arrangements should be instigated for separate collection and disposal.

- Contact your local waste collection body for more detailed recycling information.

- In case of illicit disposal, sanctions will be levied on transgressors.

## RoHS

This device, including all its components, subassemblies and the consumable materials that are an integral part of the product, has been manufactured in compliance with the European directive 2002/95/EC known as the RoHS directive (Restrictions on the use of certain Hazardous Substances). This directive targets the reduction of certain hazardous substances previously used in electrical and electronic equipment (EEE).

## **Technical Assistance**

If you have any technical questions, cannot isolate a problem with your device, or have any enquiry about repair and returns policies, contact your local Eurotech Technical Support Team.

See Eurotech Worldwide Presence, page 33 for full contact details.

## **Transportation**

When transporting any module or system, for any reason, it should be packed using anti-static material and placed in a sturdy box with enough packing material to adequately cushion it.

#### Warning:

Any product returned to Eurotech that is damaged due to inappropriate packaging will not be covered by the warranty.

## **Conventions**

The following table describes the conventions for signal names used in this document.

| Convention | Explanation                          |  |

|------------|--------------------------------------|--|

| GND        | Digital ground plane                 |  |

| #          | Active low signal                    |  |

| _P         | Positive signal in differential pair |  |

| _N         | Negative signal in differential pair |  |

The following table describes the abbreviations for direction and electrical characteristics of a signal used in this document.

| Туре     | Explanation                                                       |

|----------|-------------------------------------------------------------------|

| I        | Signal is an input to the system                                  |

| 0        | Signal is an output from the system                               |

| 10       | Signal may be input or output                                     |

| P        | Power and ground                                                  |

| 2.5      | 2.5 V signal level                                                |

| 3.3      | 3.3 V signal level                                                |

| 5        | 5 V signal level                                                  |

| Α        | Analog signal                                                     |

| HDMI     | Compliant with High-Definition Multimedia Interface Specification |

| LVDS     | Low Voltage Differential Signalling                               |

| MIPI     | Compliant with MIPI Specification                                 |

| NC       | No Connection                                                     |

| OD       | Open-drain                                                        |

| PCle     | Compliant with PCI Express v2.0 Specification                     |

| Reserved | Use is reserved to Eurotech                                       |

| SATA     | Compliant with SATA-2 Specification                               |

| USB      | Compliant with Universal Serial Bus 2.0 Specification             |

Some signals include termination on the CPU-301-16 or carrier board. The following table describes the abbreviations that specify the signal termination.

| Termination | Explanation                               |  |

|-------------|-------------------------------------------|--|

| PU          | Pull-up resistor to the specified voltage |  |

| PD          | Pull-down resistor                        |  |

| R           | Series resistor                           |  |

| С           | Series capacitor                          |  |

110127-50001 (7)

## **Product Overview**

The CPU-301-16 Development Kit provides a development platform for the CPU-301-16 and a reference for custom carrier board design. The kit consists of the following components:

- CPU-301-16 with CPU-301-16 Development Kit carrier board

- 10.4-inch TFT LCD with SVGA resolution (800 x 600, 6-bit color) and cable

- · CCFL backlight inverter and cable

- 4-wire resistive touch panel and cable

- · SD card

- 12 VDC adapter and AC cord

- · Plexiglas mounting

Please make sure you have received all the components before you begin your development. For details about getting started, refer to the *CPU-301-16 Development Kit Quick Start (Eurotech document #110127-5001)*.

As a development platform, this kit allows you to become familiar with the CPU-301-16 functionality prior to customization for your specific application. Utilize the development kit to validate your proposed design for both software and hardware. This type of testing also allows you to validate your operating system image with all required drivers loaded.

To provide flexibility and allow development across a broad spectrum of end-use applications, the CPU-301-16 Development Kit carrier board maximizes the CPU-301-16 functionality and implements many industry-standard interfaces. This configuration provides a valuable reference for your application-specific carrier board. Use Eurotech's carrier board as a starting point for your design. Using the same connectivity to the module and the same components will minimize the time spent in debugging your new design.

In addition to the CPU-301-16 Development Kit, Eurotech provides a variety of services to ensure that your CPU-301-16-based product is up and running from the first prototype release. Stay in contact with your sales and support representatives throughout your development cycle to ensure a complete and robust solution with which to move forward.

## **Block Diagram**

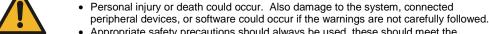

The following diagram illustrates the system organization of the CPU-301-16 Development Kit. Functionality provided by the CPU-301-16 is included in the dark blue section, while functionality provided by the carrier board is included in the light blue-gray section. Dotted lines indicate options.

Figure 1. CPU-301-16 Development Kit Block Diagram

## **Features**

The following table describes the features of the CPU-301-16 Development Kit and how the design partitions these features across the CPU-301-16 and carrier board.

| Feature                 | CPU-301-16                                    | Carrier Board                                                       |

|-------------------------|-----------------------------------------------|---------------------------------------------------------------------|

| Processor               | Freescale™ i.MX 6Solo,                        | Boot mode configuration switches                                    |

|                         | Freescale™ i.MX 6DualLite,                    | C C                                                                 |

|                         | Freescale™ i.MX 6Dual, or                     |                                                                     |

|                         | Freescale™ i.MX 6Quad                         |                                                                     |

| On-board Memory         | DDR-3 DRAM (512MB-4GB)                        |                                                                     |

|                         | RAW NAND flash device (125MB–64GB)            |                                                                     |

| Carial ATA (CATA)       | eMMC flash device (2GB–64GB)                  | CATA handar                                                         |

| Serial ATA (SATA)       | SATA bus (i.MX 6Dual/6Quad)                   | SATA header                                                         |

| Secure Digital (SD)     | SD interface (8-bit)                          | with AC coupling and ESD protection microSD socket (4-bit)          |

| Secure Digital (SD)     | SD interface (6-bit) SD interface (4-bit)     | with power switch                                                   |

|                         | OB Interface (4 bit)                          | SD socket (4-bit)                                                   |

|                         |                                               | with power switch                                                   |

| PCI Express (PCIe)      | PCIe one lane port                            | Mini PCle socket (PCle, I <sup>2</sup> C, USB, SIM, LEDs)           |

| : 0: 2xp: 000 (: 0.0)   | Total dila port                               | with AC coupling                                                    |

| Universal Serial Bus    | USB 2.0 host port signals                     | USB Hub providing 4 USB host ports                                  |

| (USB)                   | USB 2.0 OTG port signals                      | 3 x USB 2.0 host socket (USB Type A)                                |

| •                       | , ,                                           | with host power supply, current limiter, and                        |

|                         |                                               | over-voltage protection                                             |

|                         |                                               | (optional USB host headers)                                         |

|                         |                                               | 1 x USB 2.0 OTG port socket (Mini USB Type B)                       |

|                         |                                               | with EMI/ESD protection                                             |

| Serial Ports            | Up to four TTL-level serial ports:            | EIA-232 and EIA-485 transceivers                                    |

|                         | 8-wire                                        | 1 x EIA-232 header, 8-wire                                          |

|                         | 4-wire                                        | (shared with debug port on GPIO header)                             |

|                         | Up to two 4-wire (shared with CMOS Camera)    | 1 x EIA-232/485 header, 4-wire                                      |

|                         | (Shared with Civios Camera)                   | 1 x EIA-232 and EIA-232/485 header,4-wire (shared with CMOS Camera) |

| Ethernet                | Gigabit Ethernet                              | RJ-45 socket                                                        |

| Luiernet                | with physical layer transceiver               | with built-in magnetics, integrated termination,                    |

|                         | with physical layer transcerver               | and status LEDs                                                     |

| Controller Area Network | 2 x CAN 2.0 bus signals                       | 2 x CAN 2.0 bus headers                                             |

| (CAN)                   |                                               | with level translator, transceiver, common mode                     |

| ,                       |                                               | filter, and ESD protection                                          |

| I <sup>2</sup> C Bus    | General-purpose I <sup>2</sup> C bus          | On-board I <sup>2</sup> C devices                                   |

|                         | with bus master                               | and external connection on GPIO header                              |

|                         | HDMI I <sup>2</sup> C bus                     | Included on HDMI Micro socket                                       |

|                         | with bus master                               |                                                                     |

| SPI Bus                 | General-purpose SPI bus                       | External connection on GPIO header                                  |

|                         | with bus master                               |                                                                     |

| Display                 | Support for up to two (i.MX 6Solo/6Dual Lite) | Digital display header                                              |

|                         | or four (i.MX 6Dual/6Quad) simultaneous       | with buffers, power switch, termination, and                        |

|                         | displays Digital (16-, 18-, or 24-bit RGB)    | EMI protection 2 x LVDS display headers                             |

|                         | Two LVDS (18- or 24-bit)                      | with power switch and EMI/ESD protection                            |

|                         | HDMI v1.4                                     | HDMI Micro socket                                                   |

|                         | MIPI DSI, two lanes                           | with HDMI Transmitter Port Protection and                           |

|                         | Backlight control signals                     | Interface device                                                    |

|                         |                                               | MIPI DSI header                                                     |

|                         |                                               | with EMI/ESD protection                                             |

|                         |                                               | 3 x backlight headers for intensity and on/off                      |

| Camera Sensors          | CMOS Camera (8-bit)                           | CMOS Camera header                                                  |

|                         | MIPI CSI, four lanes                          | with level translator for clock signal and                          |

|                         |                                               | ESD protection                                                      |

|                         |                                               | MIPI Camera header                                                  |

|                         |                                               | with level translator for I <sup>2</sup> C bus and                  |

|                         | T                                             | EMI/ESD protection                                                  |

| User Interface          | Touch panel controller SPI bus                | Touch panel header                                                  |

|                         | with bus master                               | with touch panel controller                                         |

|                         | 8 x 8 Keypad/GPIO signals                     | 8x8 keypad/GPIO header                                              |

|                         |                                               |                                                                     |

|                         |                                               | with termination and ESD protection                                 |

|                         |                                               | 3 x buttons (Reset, Sleep, and User) 3 x LEDs                       |

| Feature           | CPU-301-16                                                                            | Carrier Board                                                                                                                     |

|-------------------|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| Audio             | Digital audio CODEC interface<br>Sony Philips Digital Interconnect Format<br>(S/PDIF) | Stereo CODEC with supporting circuitry for<br>Line output header<br>Speaker header<br>Microphone header                           |

| GPIO              | 5 x GPIO                                                                              | GPIO header with termination and ESD protection GPIO expansion for LED control                                                    |

| System Monitoring |                                                                                       | Temperature, voltage, and current sensors Accelerometer Real-time clock and battery                                               |

| Power Supply      | 3.3 V main power input supplied by carrier board Integrated power management          | 12 V main power input<br>supplied by 100-240 VAC power adapter<br>On-board power supplies and power management<br>Power state LED |

Table 1. CPU-301-16 Development Kit Features

## **Related Documents**

This manual describes the connectivity of Eurotech's carrier board and is intended for software application developers and system integrators.

For instructions to use the development kit, refer to the *CPU-301-16 Development Kit Quick Start* (Eurotech #110125-5001).

For detailed information about the CPU-301-16, refer to the CPU-301-16 Design-In Guide. (Eurotech #110127-4000).

Check the Eurotech support site (<a href="http://support.eurotech-inc.com/">http://support.eurotech-inc.com/</a>) for errata reports and for the latest releases of these documents.

# Connectors, Switches, Jumpers, and Indicators

## **Identifying Connectors**

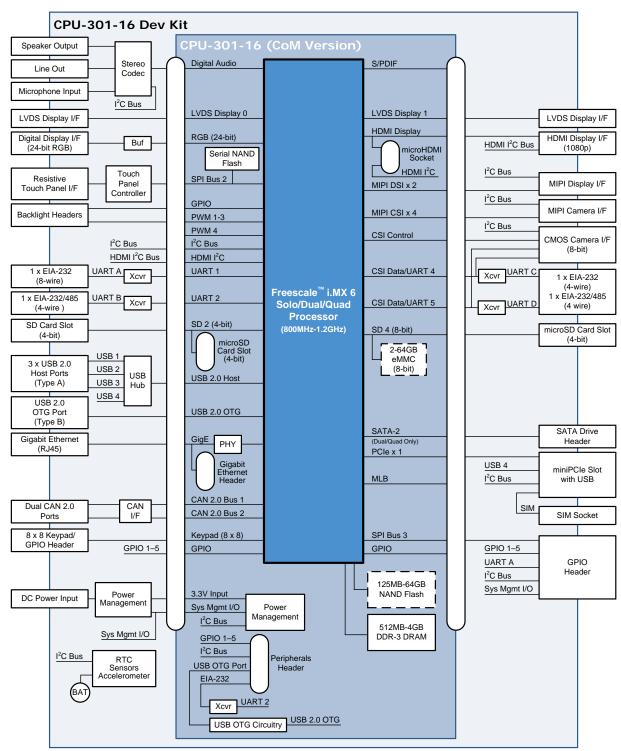

The following diagram illustrates the location and numbering of the connectors on the carrier board. The CPU-301-16 mates to two docking connectors, J1 and J2, which lie under the module when installed.

Figure 2. Connector Location, Top View

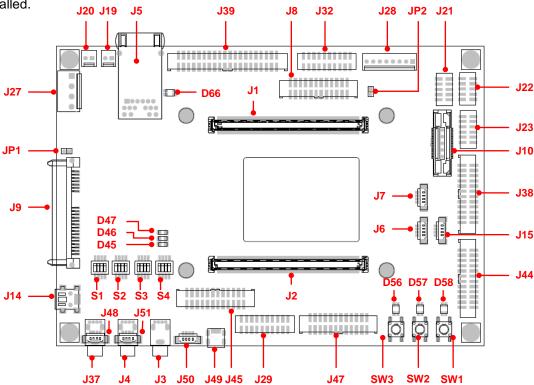

Figure 3. Connector Location, Bottom View

## Switches, Indicators, and Jumpers

This section describes various switches, indicators, and jumpers on the carrier board.

### **Boot Configuration**

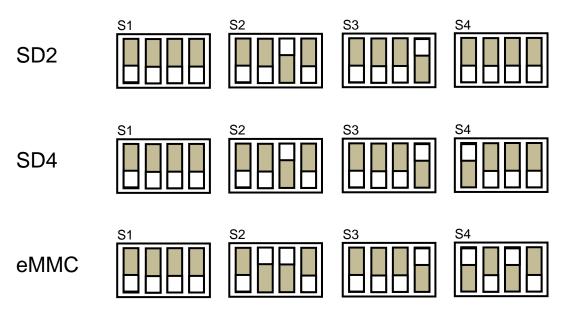

### S1-S4: Boot Configuration Switches

The configuration switches on the carrier board are used to select a specific boot device using the processor's BOOT\_CFG signals when the module is configured for Internal Boot mode. Two jumpers located on the CPU-301-16 module select the boot mode. For a detailed explanation of Boot Mode Configuration, refer to the *CPU-301-16 Design-In Guide*.

The following table describes the mapping of the BOOT\_CFG signals to the configuration switches. When the switch is in an open position, the BOOT\_CFG signal is a low logic-level. When the switch is in a closed position, the BOOT\_CFG signal is a high logic-level.

| Switch | Boot Configuration Signal Name |

|--------|--------------------------------|

| S1 1   | BOOT_CFG1_0                    |

| S1 2   | BOOT_CFG1_1                    |

| S1 3   | BOOT_CFG1_2                    |

| S1 4   | BOOT_CFG1_3                    |

| S2 1   | BOOT_CFG1_4                    |

| S2 2   | BOOT_CFG1_5                    |

| S2 3   | BOOT_CFG1_6                    |

| S2 4   | BOOT_CFG1_7                    |

| S3 1   | BOOT_CFG2_0                    |

| S3 2   | BOOT_CFG2_1                    |

| S3 3   | BOOT_CFG2_2                    |

| S3 4   | BOOT_CFG2_3                    |

| S4 1   | BOOT_CFG2_4                    |

| S4 2   | BOOT_CFG2_5                    |

| S4 3   | BOOT_CFG2_6                    |

| S4 4   | BOOT_CFG2_7                    |

Table 2. Boot Configuration Switches

## **Default Boot Configuration Setting**

The following BOOT CFG signals are set by populating various on-board resistors. The following table describes the default setting. If your application requires different settings, contact your local Eurotech representative.

| Boot Configuration Signal Name | Logic-level |

|--------------------------------|-------------|

| BOOT_CFG4_0                    | High        |

| BOOT_CFG4_1                    | Low         |

| BOOT_CFG4_2                    | Low         |

| BOOT_CFG4_3                    | Low         |

| BOOT_CFG4_4                    | High        |

| BOOT_CFG4_5                    | Low         |

| BOOT_CFG4_7                    | Low         |

Table 3. Default Boot Configuration Settings

The following diagram shows the carrier board reference DIP switch settings by boot source.

Figure 4. Carrier Board Reference Dip Switch Settings

#### Carrier Board Switches

#### SW1: Reset

SW1 is the reset button for the CPU-301-16 Development Kit. Pressing SW1 initiates a hardware reset of module circuitry including the processor. Press this button to restart the system without cycling power.

#### SW2: Sleep

SW2 is the sleep button for the CPU-301-16 Development Kit.

#### SW3: Button

SW3 is a general-purpose button for the CPU-301-16 Development Kit. The output is connected to GPIO6\_IO3/GPIO\_BUTTON (CPU-301-16 module J1 B30).

### Carrier Board LED Indicators

### D56: GPIO-controlled LED

The carrier board includes one general-purpose red/green light-emitting diode (LED) that is controlled by GPIO signals from the CPU-301-16 module. The following table describes the mapping of the control signals to the LEDs.

| LED | Input | Control Signal                   |

|-----|-------|----------------------------------|

| D56 | Red   | GPIO5_IO16/GPIO_LED_RED (J1 B58) |

| D30 | Green | GPIO7_IO2/GPIO_LED_GRN (J1 B59)  |

#### D57 and D58: I2C bus-controlled LEDs

The carrier board includes two general-purpose red/green light-emitting diodes (LEDs) that are software-controlled using the I<sup>2</sup>C bus. For the I<sup>2</sup>C bus address, see General-Purpose I<sup>2</sup>C Bus Addresses, page 30. The following table describes the mapping of the control signals to the LEDs.

| LED | Input | Control Signal          |

|-----|-------|-------------------------|

| D57 | Red   | GPIO Expansion Output 0 |

| ופט | Green | GPIO Expansion Output 1 |

| D58 | Red   | GPIO Expansion Output 2 |

| D30 | Green | GPIO Expansion Output 3 |

### D66: Power/Sleep LED

The Power/Sleep LED indicates the operational mode and power status as described in the following table.

| Color | Mode  | Power Status |

|-------|-------|--------------|

| Green | Run   | Power on     |

| Red   | Sleep | Power on     |

### D45-D47: Mini PCle 0 Status LEDs

The three Mini PCIe Status LEDs indicates network connectivity as described in the following table.

| LED | Туре  | Description                                     |

|-----|-------|-------------------------------------------------|

| D45 | Green | Indicates Wireless Personal Area Network (WPAN) |

| D46 | Green | Indicates Wireless Local Area Network (WLAN)    |

| D47 | Green | Indicates Wireless Wide Area Network (WWAN)     |

#### **Ethernet LEDs**

The LED on the left side of Ethernet socket J5 indicates connection as follows.

| Operation | Speed (Mbps)                |

|-----------|-----------------------------|

| On        | On indicates an active link |

| Off       | No link                     |

The LED on the right side of Ethernet socket J5 indicates connection and activity as follows.

| Operation | Link/Activity                        |

|-----------|--------------------------------------|

| On        | Blinking indicates Ethernet activity |

| Off       | No activity                          |

## **Carrier Board Jumpers**

JP1: 5V

Type: 2-post header, 2 mm

Jumper JP1 is reserved for future use.

## JP2: Touch Panel Configuration Jumper

Type: 2-post header, 2 mm

Jumper JP2 configures the development kit for support of 4-, 5- and 8-wire touch panels as follows.

| Jumper Setting | Configuration                   |  |

|----------------|---------------------------------|--|

| 1-2            | 5-wire only support             |  |

| NC             | 4- and 8-wire support (default) |  |

## **Signal Headers**

The following tables describe the electrical signals available on the connectors of the carrier board. Each section provides relevant details about the connector including part numbers, mating connectors, signal descriptions, and references to related sections.

For the location of the connectors, see Identifying Connectors, page 12.

### J1: Docking Connector

The CPU-301-16 connector J1 mates to the carrier board connector J1. For details about this connector, refer to the *CPU-301-16 Design-In Guide 110127-4000*.

## J2: Docking Connector

The CPU-301-16 connector J2 mates to the carrier board connector J2. For details about this connector, refer to the *CPU-301-16 Design-In Guide 110127-4000*.

### J3: USB Host 1

Board connector: USB Type A receptacle, Molex 89485-8000

Mating connector: USB Type A plug

The USB socket J3 provides USB Host 1 supporting the USB 2.0 specification at High Speed (480 Mbps). The connector shield is tied to chassis ground. USB Host 1 is also available on header J50, page 28.

### J4: USB Host 2

Board connector: USB Type A receptacle, Molex 89485-8000

Mating connector: USB Type A plug

The USB socket J4 provides USB Host 2 supporting the USB 2.0 specification at High Speed (480 Mbps). The connector shield is tied to chassis ground.

#### J5: Gigabit Ethernet

Board connector: RJ-45 socket with LEDs, Pulse Engineering JK0-0136NL

Mating connector: RJ-45 plug

Socket J5 provides a direct connection to a Gigabit Ethernet network for 10Base-T, 100Base-TX, and 1000Base-T applications. The connector shield is tied to chassis ground.

### J6: Line Out

Board connector: 1x4 shrouded header, 1.25 mm, Molex 53398-0471

Mating connector: Molex 51021-0400 series housing

Header J6 provides a stereo line output.

| Pin | Name           | Type | Description               |

|-----|----------------|------|---------------------------|

| 1   | LINE_OUT_L     | AO   | Line out 1, left channel  |

| 2   | LINE_OUT_SENSE | Al   | Sense                     |

| 3   | LINE_OUT_R     | AO   | Line out 1, right channel |

| 4   | AUD_AGND2      | Р    | Audio ground              |

110127-50001

## J7: Microphone

Board connector: 1x4 shrouded header, 1.25 mm, Molex 53398-0471

Mating connector: Molex 51021-0400 series housing

Header J7 provides connection to a microphone.

| Pin | Name      | Туре | Description               |

|-----|-----------|------|---------------------------|

| 1   | MIC_IN_L  | Al   | Microphone, left channel  |

| 2   | AUD_AGND3 | Р    | Audio ground              |

| 3   | MIC_IN_R  | Al   | Microphone, right channel |

| 4   | AUD_AGND1 | Р    | Audio ground              |

## J8: Keypad

Board connector: 2x12 shrouded header, 2.00 mm, Samtec STMM-112-02-T-D-SM

Mating connector: Samtec TCSD series IDC cable assembly socket

The CPU-301-16 Development Kit provides sixteen signals that can be used to support an 8x8 keypad or as general-purpose inputs and outputs (GPIO). These keypad/GPIO signals are available on connector J8.

| Pin | Name        | Type | Description      |

|-----|-------------|------|------------------|

| 1   | GND         | Р    | Ground           |

| 2   | KP_COL0_OUT | IO   | Keypad, Column 0 |

| 3   | KP_ROW0_OUT | IO   | Keypad, Row 0    |

| 4   | KP_COL1_OUT | IO   | Keypad, Column 1 |

| 5   | KP_ROW1_OUT | IO   | Keypad, Row 1    |

| 6   | KP_COL2_OUT | IO   | Keypad, Column 2 |

| 7   | KP_ROW2_OUT | Ю    | Keypad, Row 2    |

| 8   | KP_COL3_OUT | IO   | Keypad, Column 3 |

| 9   | KP_ROW3_OUT | IO   | Keypad, Row 3    |

| 10  | KP_COL4_OUT | IO   | Keypad, Column 4 |

| 11  | GND         | Р    | Ground           |

| 12  | GND         | Р    | Ground           |

| 13  | KP_ROW4_OUT | Ю    | Keypad, Row 4    |

| 14  | KP_COL5_OUT | Ю    | Keypad, Column 5 |

| 15  | KP_ROW5_OUT | IO   | Keypad, Row 5    |

| 16  | KP_COL6_OUT | Ю    | Keypad, Column 6 |

| 17  | KP_ROW6_OUT | IO   | Keypad, Row 6    |

| 18  | KP_COL7_OUT | IO   | Keypad, Column 7 |

| 19  | KP_ROW7_OUT | Ю    | Keypad, Row 7    |

| 20  | GND         | Р    | Ground           |

| 21  | GND         | Р    | Ground           |

| 22  | NC          |      |                  |

| 23  | V_3P3V_SW   | PO   | Switched 3.3V    |

| 24  | V_3P3V_SW   | PO   | Switched 3.3V    |

#### J9: SATA

Board connector: 22-position receptacle, 1.27 mm, FCI 10029364-001LF

Mating connector: SATA plug

Header J9 provides connection to a SATA disk drive supporting the Serial ATA II Specification with data transfer rates of up to 3.0 Gbps.

110127-50001 (17)

## J10: JTAG, CMOS Camera, and GPIO

Board connector: 38-position, MICTOR receptacle, 0.025 inch, AMP 2-5767004-2

Mating connector: AMP MICTOR plug

The CPU-301-16 Development Kit provides a full IEEE1149.1 JTAG port, connection to the CMOS Camera signals, and several GPIO on connector J10.

| Pin | Name                    | Туре | Description                                       | (Note 1) |

|-----|-------------------------|------|---------------------------------------------------|----------|

| 1   | NC                      |      | No connection                                     |          |

| 2   | NC                      |      | No connection                                     |          |

| 3   | NC                      |      | No connection                                     |          |

| 4   | NC                      |      | No connection                                     |          |

| 5   | GND                     | Р    | Ground                                            |          |

| 6   | CSI_DATA_EN             | 0    | CMOS Camera, Data enable                          | J2 B12   |

| 7   | PULLDN1                 |      | Pulldown resistor, 4.7kΩ                          |          |

| 8   | PULLDN2                 |      | Pulldown resistor, 4.7kΩ                          |          |

| 9   | JTAG_RST#               | I    | JTAG, Reset                                       | J1 A23   |

| 10  | PULLDN3                 |      | Pulldown resistor, 4.7kΩ                          |          |

| 11  | JTAG_TDO                | 0    | JTAG, Test Data Out                               | J1 A26   |

| 12  | PULLUP1                 |      | Pullup resistor, 4.7kΩ to 3.3V                    |          |

| 13  | PULLDN4                 |      | Pulldown resistor, 10kΩ                           |          |

| 14  | PULLUP2                 |      | Pullup resistor, 4.7kΩ to 3.3V                    |          |

| 15  | JTAG_TCK                | I    | JTAG, Test Clock                                  | J1 A27   |

| 16  | UART1_TXD               | 0    | Serial 1, Transmit Data                           | J1 A6    |

| 17  | JTAG_TMS                | 1    | JTAG, Test Mode Select                            | J1 A24   |

| 18  | KP_ROW7                 | IO   | Keypad, Row 7                                     | J1 B40   |

| 19  | JTAG_TDI                | I    | JTAG, Test Data In                                | J1 A25   |

| 20  | KP_COL7                 | Ю    | Keypad, Column 7                                  | J1 A40   |

| 21  | JTAG_TRST#              | I    | JTAG, Test Reset                                  | J1 A22   |

| 22  | KP_ROW6                 | Ю    | Keypad, Row 6                                     | J1 B39   |

| 23  | UART5_RTS_CSI_DAT18     | 0    | Serial 5, Request To Send / CMOS Camera, Data 18  | J2 A18   |

| 24  | GPIO_USR_0 (GPIO5_IO3)  | IO   | General user I/O                                  | J1 A54   |

| 25  | UART4_CTS_CSI_DAT17     | I    | Serial 4, Clear To Send / CMOS Camera, Data 17    | J2 A17   |

| 26  | KP_ROW5                 | IO   | Keypad, Row 5                                     | J1 B38   |

| 27  | UART4_RTS_CSI_DAT16     | 0    | Serial 4, Request To Send / CMOS Camera, Data 16  | J2 A16   |

| 28  | GPIO5 IO1/GPIO nUSB RST | IO   | External USB Hub reset                            | J1 A52   |

| 29  | UART5_RXD_CSI_DAT15     | 1    | Serial 5, Receive Data /<br>CMOS Camera, Data 15  | J2 A15   |

| 30  | PULLDN5                 |      | Pulldown resistor, 4.7kΩ                          |          |

| 31  | UART5_TXD_CSI_DAT14     | 0    | Serial 5, Transmit Data /<br>CMOS Camera, Data 14 | J2 A14   |

| 32  | PULLDN6                 |      | Pulldown resistor, 4.7kΩ                          |          |

| 33  | UART4_RXD_CSI_DAT13     | 1    | Serial 4, Receive Data /                          | J2 A13   |

|     | 5 1_10.5_501_5/(110     |      | CMOS Camera, Data 13                              | 02,110   |

| 34  | PULLUP3                 |      | Pullup resistor, 4.7kΩ to 3.3V                    |          |

| 35  | UART4_TXD_CSI_DAT12     | 0    | Serial 4, Transmit Data /<br>CMOS Camera, Data 12 | J2 A12   |

| 36  | CSI_HSYNC               | 0    | CMOS Camera, Horizontal sync                      | J2 B13   |

| 37  | UART1_RXD               | 1    | Serial 1, Receive Data                            | J1 A4    |

| 38  | CSI_VSYNC               | 0    | CMOS Camera, Vertical sync                        | J2 B14   |

Notes:

1. Signals connect directly to the docking connectors specified.

## J11: JTAG (Option)

Board connector: 2x5 socket strip, 0.05 inch, Samtec CLP-105-02-L-D-A

Mating connector: Terminal strip

As an option, header J11 can be populated to provide a JTAG connection.

| Pin | Name       | Туре | Description            |

|-----|------------|------|------------------------|

| 1   | JTAG_RST#  | I    | JTAG, Reset            |

| 2   | JTAG_TRST# | I    | JTAG, Test Reset       |

| 3   | JTAG_TMS   | I    | JTAG, Test Mode Select |

| 4   | GND        | Р    | Ground                 |

| 5   | JTAG_TCK   | I    | JTAG, Test Clock       |

| 6   | GND        | Р    | Ground                 |

| 7   | JTAG_TDI   | I    | JTAG, Test Data In     |

| 8   | GND        | Р    | Ground                 |

| 9   | JTAG_TDO   | 0    | JTAG, Test Data Out    |

| 10  | V_3P3V     | PO   | 3.3V                   |

## J13: Mini PCle (x1)

Board connector: 52-pin MiniCard, Molex 67910-0001

Mating connector: Mini PCIe card

Socket J13 provides a direct PCIe v2.0, on lane connection to the CPU-301-16 module. The socket accepts Mini PCIe x1 cards and supports a SIM card interface (J43, page 25).

### J15: Speaker

Board connector: 1x4 shrouded header, 1.25 mm, Molex 53398-0471

Mating connector: Molex 51021-0400 series housing

Header J15 provides the connection to a stereo line output capable of driving powered speakers.

| Pin | Name         | Туре | Description                     |

|-----|--------------|------|---------------------------------|

| 1   | SPKR_OUT_R_P | AO   | Speaker, right channel positive |

| 2   | SPKR_OUT_R_N | AO   | Speaker, right channel negative |

| 3   | SPKR_OUT_L_P | AO   | Speaker, left channel positive  |

| 4   | SPKR_OUT_L_N | AO   | Speaker, left channel negative  |

## J14: USB OTG

Board connector: Mini USB Type B receptacle, FCI 10033526-N3215LF

Mating connector: Mini USB Type B plug

The USB socket J14 provides a USB OTG port supporting the USB 2.0 specification at High Speed (480 Mbps). USB functionality is automatically selected by the state of the OTG\_ID pin in the cable connection. Generic devices automatically drive the OTG\_ID pin to ground to cause the port to assume Host functionality. External host port connections must leave this pin open to cause this port to assume Client functionality.

The connector shield is tied to chassis ground.

### J19: CAN

Board connector: 2-pin header, 0.1-inch, Molex 22-23-2021 Mating connector: crimp housing, Molex 22-01-2021

Header J19 supplies a CAN bus supporting the CAN 2.0B Protocol Specification with bit rates up to 1 Mbps.

| Pin | Name       | Type | Description |

|-----|------------|------|-------------|

| 1   | CAN1_H_OUT | IO   | CAN 1       |

| 2   | CAN1_L_OUT | 10   | CANT        |

### J20: CAN

Board connector: 2-pin header, 0.1-inch, Molex 22-23-2021 Mating connector: crimp housing, Molex 22-01-2021

Header J20 supplies a CAN bus supporting the CAN 2.0B Protocol Specification with bit rates up to 1 Mbps.

|   | Pin | Name       | Туре | Description |

|---|-----|------------|------|-------------|

| ľ | 1   | CAN2_H_OUT | Ю    | CAN 2       |

|   | 2   | CAN2_L_OUT |      |             |

### J21: Serial A

Board connector: 2x5 header, 2 mm, Molex 87832-1006

Mating connector: Molex 87568 series wire-to-board IDT housing

Header J21 supports a full-feature EIA-232 serial port.

| Pin | Name  | Туре | Description         |

|-----|-------|------|---------------------|

| 1   | DCD_A | I    | Data Carrier Detect |

| 2   | DSR_A | I    | Data Set Ready      |

| 3   | RXD_A | I    | Receive Data        |

| 4   | RTS_A | 0    | Request To Send     |

| 5   | TXD_A | 0    | Transmit Data       |

| 6   | CTS_A | I    | Clear To Send       |

| 7   | DTR_A | 0    | Data Terminal Ready |

| 8   | RI_A  | I    | Ring Indicator      |

| 9   | GND   | Р    | Ground              |

| 10  | NC    |      |                     |

## J22: Serial B

Board connector: 2x5 header, 2 mm, Molex 87832-1006

Mating connector: Molex 87568 series wire-to-board IDT housing

Header J22 supports an EIA-232/485 serial port.

| Pin | Name         | Type | Description     |                             |

|-----|--------------|------|-----------------|-----------------------------|

|     |              |      | EIA-232         | EIA-485                     |

| 1   | NC           |      |                 |                             |

| 2   | NC           |      |                 |                             |

| 3   | RXD_485RXN_B | I    | Receive Data    | Inverting Receive Data      |

| 4   | RTS_485TXP_B | 0    | Request To Send | Non-inverting Transmit Data |

| 5   | TXD_485TXN_B | 0    | Transmit Data   | Inverting Transmit Data     |

| 6   | CTS_485RXP_B | I    | Clear To Send   | Non-inverting Receive Data  |

| 7   | NC           |      |                 |                             |

| 8   | NC           |      |                 |                             |

| 9   | GND          | Р    | Ground          | Ground                      |

| 10  | NC           |      |                 |                             |

### J23: Serial C and Serial D

Board connector: 2x6 header, 2 mm, Molex 87832-1222

Mating connector: Molex 87568 series wire-to-board IDT housing

Header J23 supports a 4-wire EIA-232 serial port and an EIA-232/485 serial port.

| Pin | Name         | Туре | Description     |                             |

|-----|--------------|------|-----------------|-----------------------------|

|     |              |      | EIA-232         | EIA-485                     |

| 1   | RXD_D        | I    | Receive Data    |                             |

| 2   | RTS_D        | 0    | Request To Send |                             |

| 3   | TXD_D        | 0    | Transmit Data   |                             |

| 4   | CTS_D        | I    | Clear To Send   |                             |

| 5   | GND          | Р    | Ground          | Ground                      |

| 6   | GND          | Р    | Ground          | Ground                      |

| 7   | RXD_485RXN_C | I    | Receive Data    | Inverting Receive Data      |

| 8   | RTS_485TXP_C | 0    | Request To Send | Non-inverting Transmit Data |

| 9   | TXD_485TXN_C | 0    | Transmit Data   | Inverting Transmit Data     |

| 10  | CTS_485RXP_C | I    | Clear To Send   | Non-inverting Receive Data  |

| 11  | GND          | Р    | Ground          | Ground                      |

| 12  | GND          | Р    | Ground          | Ground                      |

## J27: DC Power Input

Board connector: 1x4 header, 3.96 mm, AMP 1-1318300-4 Mating connector: AMP 1-1123722-4 crimp housing

Header J27 accepts +12 VDC input power from an external supply such as the AC power adapter included with the CPU-301-16 Development Kit.

| Pin | Name | Туре | Description                |

|-----|------|------|----------------------------|

| 1   | GND  | Р    | Ground                     |

| 2   | GND  | Р    | Ground                     |

| 3   | V_IN | PI   | Input power (12 V nominal) |

| 4   | V_IN | PI   | Input power (12 V nominal) |

#### Warning:

Disconnect the power input before removing the module. Removing the module from a powered carrier board may result in damage to both the carrier board and to the module.

## J28: Touch Panel (8-wire)

Board connector: 8-pin header, 2.54 mm, Molex 22-11-2082

Mating connector: Molex 22-01-2087 crimp housing

Header J28 supports an 8-wire touch panel. Standard CPU-301-16 Development Kits include a 4-wire touch panel.

| Pin | Name  | Туре | 8-Wire       | Description |

|-----|-------|------|--------------|-------------|

| 1   | MX_LL | AIO  | Left         |             |

| 2   | PX_UR | AIO  | Right        |             |

| 3   | PY_UL | AIO  | Bottom       |             |

| 4   | MY_LR | AIO  | Top          | Touch panel |

| 5   | SXM   | AIO  | Left sense   | rouch paner |

| 6   | SXP   | AIO  | Right sense  |             |

| 7   | SYM   | AIO  | Top sense    |             |

| 8   | SYP   | AIO  | Bottom sense |             |

## J29: LVDS Display 1

Board connector: 2x10 shrouded header, 2.00 mm, Molex 87832-2020 Mating connector: Molex 87568 series wire-to-board IDT housing

Header J29 provides connection to a LVDS display.

| Pin | Name            | Туре | Description               |

|-----|-----------------|------|---------------------------|

| 1   | V_LVDS1_PWR     | PO   | Software-controlled 3.3 V |

| 2   | V_LVDS1_PWR     | PO   | Software-controlled 3.3 V |

| 3   | LVDS1_OUT_TX0_N | 0    | LVDS data 0, negative     |

| 4   | GND             | Р    | Ground                    |

| 5   | GND             | Р    | Ground                    |

| 6   | LVDS1_OUT_TX0_P | 0    | LVDS data 0, positive     |

| 7   | LVDS1_OUT_TX1_P | 0    | LVDS data 1, positive     |

| 8   | LVDS1_OUT_TX1_N | 0    | LVDS data 1, negative     |

| 9   | LVDS1_OUT_TX2_N | 0    | LVDS data 2, negative     |

| 10  | GND             | Р    | Ground                    |

| 11  | GND             | Р    | Ground                    |

| 12  | LVDS1_OUT_TX2_N | 0    | LVDS data 2, negative     |

| 13  | LVDS1_OUT_CLK_P | 0    | LVDS clock, positive      |

| 14  | LVDS1_OUT_CLK_N | 0    | LVDS clock, negative      |

| 15  | GND             | Р    | Ground                    |

| 16  | GND             | Р    | Ground                    |

| 17  | LVDS1_OUT_TX3_N | 0    | LVDS data 3, negative     |

| 18  | LVDS1_OUT_TX3_P | 0    | LVDS data 3, positive     |

| 19  | GND             | Р    | Ground                    |

| 20  | GND             | Р    | Ground                    |

#### J31: microSD Card

Board connector: microSD card socket, Molex 502570-0893

Mating connector: microSD card

The CPU-301-16 Development Kit provides a microSD card (4-bit) socket on J31 for memory and I/O expansion. Power (3.3 V only) to this socket is software-controlled.

#### J30: SD Card

Board connector: SD card socket, Molex 67913-0002

Mating connector: SD card

The CPU-301-16 Development Kit provides a SD card (4-bit) socket on J30 for memory and I/O expansion. Power (3.3 V only) to this socket is software-controlled.

### J32: LVDS Display 0

Board connector: 2x10 shrouded header, 2.00 mm, Molex 87832-2020 Mating connector: Molex 87568 series wire-to-board IDT housing

Header J32 provides connection to a LVDS display.

| Pin | Name            | Туре | Description               |

|-----|-----------------|------|---------------------------|

| 1   | V_LVDS0_PWR     | PO   | Software-controlled 3.3 V |

| 2   | V_LVDS0_PWR     | PO   | Software-controlled 3.3 V |

| 3   | LVDS0_OUT_TX0_N | 0    | LVDS data 0, negative     |

| 4   | GND             | Р    | Ground                    |

| 5   | GND             | Р    | Ground                    |

| 6   | LVDS0_OUT_TX0_P | 0    | LVDS data 0, positive     |

| 7   | LVDS0_OUT_TX1_P | 0    | LVDS data 1, positive     |

| 8   | LVDS0_OUT_TX1_N | 0    | LVDS data 1, negative     |

| 9   | LVDS0_OUT_TX2_N | 0    | LVDS data 2, negative     |

| 10  | GND             | Р    | Ground                    |

| 11  | GND             | Р    | Ground                    |

| 12  | LVDS0_OUT_TX2_N | 0    | LVDS data 2, negative     |

| 13  | LVDS0_OUT_CLK_P | 0    | LVDS clock, positive      |

| 14  | LVDS0_OUT_CLK_N | 0    | LVDS clock, negative      |

| Pin | Name            | Туре | Description           |

|-----|-----------------|------|-----------------------|

| 15  | GND             | Р    | Ground                |

| 16  | GND             | Р    | Ground                |

| 17  | LVDS0_OUT_TX3_N | 0    | LVDS data 3, negative |

| 18  | LVDS0_OUT_TX3_P | 0    | LVDS data 3, positive |

| 19  | GND             | Р    | Ground                |

| 20  | GND             | Р    | Ground                |

## J37: USB Host 3

Board connector: USB Type A receptacle, Molex 89485-8000

Mating connector: USB Type A plug

The USB socket J37 provides USB Host 3 supporting the USB 2.0 specification at High Speed (480 Mbps). The connector shield is tied to chassis ground.

#### J38: GPIO

Board connector: 2x12 shrouded header, 2.00 mm, Samtec STMM-112-02-T-D-SM

Mating connector: Samtec TCSD series IDC cable assembly socket

Header J38 provides connections to the debug port, general-purpose I<sup>2</sup>C bus, general-purpose SPI bus, general-user IO, and power control.

| Pin | Name             | Туре | Description               | Comments                        |

|-----|------------------|------|---------------------------|---------------------------------|

| 1   | TXD_B_OUT        | 0    | Debug port, Transmit Data | Note 2, TXD_485TXN_B, J22 5     |

| 2   | RXD_B_OUT        | ı    | Debug port, Receive Data  | Note 2, RXD_485RXN_B, J22 3     |

| 3   | USR_SCL_OUT      | 0    | I <sup>2</sup> C clock    | Note 2, I2C3_SCL, J1 B8         |

| 4   | USR_SDA_OUT      | Ю    | I <sup>2</sup> C data     | Note 2, I2C3_SDA, J1 B7         |

| 5   | SPI3_MISO_OUT    |      | SPI 3, Master input       | Note 2, SPI3_MISO, J2 A2        |

| 6   | SPI3_MOSI_OUT    | 0    | SPI 3, Master output      | Note 2, SPI3_MOSI, J2 A3        |

| 7   | SPI3_RDY_OUT     |      | SPI 3, Ready              | Note 2, SPI3_RDY, J2 A4         |

| 8   | SPI3_SCLK_OUT    | 0    | SPI 3, Serial clock       | Note 2, SPI3_SCLK, J2 A5        |

| 9   | SPI3_SS0_OUT     | 0    | SPI 3, Chip select 0      | Note 2, SPI3_SS0, J2 A6         |

| 10  | GND              | Р    | Ground                    |                                 |

| 11  | GND              | Р    | Ground                    |                                 |

| 12  | RESET_BTN_OUT    | 0    | Reset                     | Connects to SW1: Reset, page 14 |

| 13  | USR_GPIO_0_OUT   | IO   | General user I/O          | Note 3, GPIO5_IO3, J1 A54       |

| 14  | USR_GPIO_1_OUT   | IO   | General user I/O          | Note 3, GPIO5_IO4, J1 A55       |

| 15  | USR_GPIO_2_OUT   | IO   | General user I/O          | Note 3, GPIO5_IO5, J1 A56       |

| 16  | USR_GPIO_3_OUT   | Ю    | General user I/O          | Note 3, GPIO5_IO6, J1 A57       |

| 17  | GND              | Р    | Ground                    |                                 |

| 18  | SLEEP_BTN_OUT    | 0    | Sleep                     | Connects to SW2: Sleep, page 14 |

| 19  | PMIC_PWR_CYCLE   | l    | Power reset               | Note 4, PMIC_PWR_CYCLE#, J1 B49 |

| 20  | GND              | Р    | Ground                    |                                 |

| 21  | ON_STATE         | 0    | Power on                  | Buffered GPIO_ON_STATE, J1 B87  |

| 22  | WDOG_TIMEOUT_OUT | 0    | Watchdog timeout          | Note 3, WDOG_TIMEOUT, J1 B89    |

| 23  | V_3P3V_SW        | PO   | Switched 3.3V             |                                 |

| 24  | V_5V_SW          | PO   | Switched 5V               |                                 |

#### Notes:

- 2. Signal connects to the connector specified through a  $22\Omega$  series resistor.

- 3. Signal connects to the connector specified through a  $1k\Omega$  series resistor.

- 4. Signal connects directly to the docking connectors specified.

## J39: Digital Display

Board connector: 2x20 shrouded header, 2.00 mm, Samtec STMM-120-02-T-D-SM

Mating connector: Samtec TCSD series IDC cable assembly socket

To support display devices such as medium resolution LCDs, the CPU-301-16 Development Kit provides a parallel digital display output on header J39.

| Pin | Name         | Туре | Description                  |

|-----|--------------|------|------------------------------|

| 1   | GND          | Р    | Ground                       |

| 2   | GND          | Р    | Ground                       |

| 3   | PNL_HSYNC    | 0    | Horizontal sync              |

| 4   | PNL_PIXCLK   | 0    | Pixel clock                  |

| 5   | PNL_VSYNC    | 0    | Vertical sync                |

| 6   | GND          | Р    | Ground                       |

| 7   | PNL_RED0     | 0    | Red 0                        |

| 8   | PNL_RED1     | 0    | Red 1                        |

| 9   | PNL_RED2     | 0    | Red 2                        |

| 10  | PNL_RED3     | 0    | Red 3                        |

| 11  | PNL_RED4     | 0    | Red 4                        |

| 12  | PNL_RED5     | 0    | Red 5                        |

| 13  | PNL_RED6     | 0    | Red 6                        |

| 14  | PNL_RED7     | 0    | Red 7                        |

| 15  | PNL_GREEN0   | 0    | Green 0                      |

| 16  | PNL_GREEN1   | 0    | Green 1                      |

| 17  | PNL_GREEN2   | 0    | Green 2                      |

| 18  | PNL_GREEN3   | 0    | Green 3                      |

| 19  | PNL_GREEN4   | 0    | Green 4                      |

| 20  | PNL_GREEN5   | 0    | Green 5                      |

| 21  | PNL_GREEN6   | 0    | Green 6                      |

| 22  | PNL_GREEN7   | 0    | Green 7                      |

| 23  | PNL_BLUE0    | 0    | Blue 0                       |

| 24  | PNL_BLUE1    | 0    | Blue 1                       |

| 25  | PNL_BLUE2    | 0    | Blue 2                       |

| 26  | PNL_BLUE3    | 0    | Blue 3                       |

| 27  | PNL_BLUE4    | 0    | Blue 4                       |

| 28  | PNL_BLUE5    | 0    | Blue 5                       |

| 29  | PNL_BLUE6    | 0    | Blue 6                       |

| 30  | PNL_BLUE7    | 0    | Blue 7                       |

| 31  | RGB_PNL_PWR  | PO   | Software-controlled 3.3V     |

| 32  | RGB_PNL_PWR  | PO   | Software-controlled 3.3V     |

| 33  | PNL_RL       | 0    | 4.7kΩ pull-up to RGB_PNL_PWR |

| 34  | PNL_UD       | 0    | 4.7kΩ pull-up to RGB_PNL_PWR |

| 35  | PNL_ENA      | 0    | Enable                       |

| 36  | PNL_CONTRAST | 0    | 4.7kΩ pull-up to RGB_PNL_PWR |

| 37  | PNL_LBIAS    | 0    | LCD Bias                     |

| 38  | NC           | _    |                              |

| 39  | GND          | Р    | Ground                       |

| 40  | GND          | Р    | Ground                       |

## J40: Backlight 0

Board connector: 7-pin header, 1.25 mm, Molex 53261-0771

Mating connector: Molex 51021-0700 crimp housing

Header J40 provides the signals to control a backlight.

| Pin | Name    | Туре | Description                         |

|-----|---------|------|-------------------------------------|

| 1   | V_BL0   | PO   | Backlight power (12 V nominal)      |

| 2   | V_BL0   | PO   | Backlight power (12 V nominal)      |

| 3   | GND     | Р    | Ground                              |

| 4   | GND     | Р    | Ground                              |

| 5   | nBL0_ON | 0    | Turns backlight on or off           |

| 6   | BL_PWM0 | 0    | Controls intensity of the backlight |

| 7   | GND     | Р    | Ground                              |

## J41: Backlight 1

Board connector: 7-pin header, 1.25 mm, Molex 53261-0771

Mating connector: Molex 51021-0700 crimp housing

Header J41 provides the signals to control a backlight.

| Pin | Name    | Туре | Description                         |

|-----|---------|------|-------------------------------------|

| 1   | V_BL1   | PO   | Backlight power (12 V nominal)      |

| 2   | V_BL1   | PO   | Backlight power (12 V nominal)      |

| 3   | GND     | Р    | Ground                              |

| 4   | GND     | Р    | Ground                              |

| 5   | nBL1_ON | 0    | Turns backlight on or off           |

| 6   | BL_PWM1 | 0    | Controls intensity of the backlight |

| 7   | GND     | Р    | Ground                              |

### J43: SIM

Board connector: SIM card socket, Molex 47553-001

Mating connector: SIM cards

The carrier board includes a standard Subscriber Identity Module (SIM) socket supporting devices requiring secure subscriber identification. This SIM interface connects to the Mini PCIe socket J13, page 19.

#### J44: CMOS Camera

Board connector: 2x12 shrouded header, 2.00 mm, Samtec STMM-112-02-T-D-SM

Mating connector: Samtec TCSD series IDC cable assembly socket

To support input from a digital camera, the CPU-301-16 Development Kit provides a parallel CMOS camera port on header J44.

| Pin | Name              | Туре | Description                                        |  |  |

|-----|-------------------|------|----------------------------------------------------|--|--|

| 1   | V_2P8V_SW         | PO   | Switched 2.8V                                      |  |  |

| 2   | V_1P5V_SW         | PO   | Switched 1.5V                                      |  |  |

| 3   | CSI_MCLK_OUT      | 0    | Clock                                              |  |  |

| 4   | V_1P8V_SW         | PO   | Switched 1.8V                                      |  |  |

| 5   | GND               | Р    | Ground                                             |  |  |

| 6   | V_3P3V_SW         | PO   | Switched 3.3V                                      |  |  |

| 7   | CSI0_DAT12_OUT    | 0    | Data 12                                            |  |  |

| 8   | CSI0_SCL_OUT      | 0    | I <sup>2</sup> C clock                             |  |  |

|     |                   |      | (Connects to general-purpose I <sup>2</sup> C bus) |  |  |

| 9   | CSI0_DAT13_OUT    | 0    | Data 13                                            |  |  |

| 10  | CSI0_SDA_OUT      | Ю    | I <sup>2</sup> C data                              |  |  |

|     |                   |      | (Connects to general-purpose I <sup>2</sup> C bus) |  |  |

| 11  | CSI0_DAT14_OUT    | 0    | Data 14                                            |  |  |

| 12  | GND               | Р    | Ground                                             |  |  |

| 13  | CSI0_DAT15_OUT    | 0    | Data 15                                            |  |  |

| 14  | CSI0_DATA_EN _OUT | 0    | Data enable                                        |  |  |

| 15  | CSI0_DAT16_OUT    | 0    | Data 16                                            |  |  |

| 16  | CSI0_HSYNC_OUT    | 0    | Horizontal sync                                    |  |  |

| 17  | CSI0_DAT17_OUT    | 0    | Data 17                                            |  |  |

| 18  | CSI0_VSYNC_OUT    |      | Vertical sync                                      |  |  |

| 19  | CSI0_DAT18_OUT    | 0    | Data 18                                            |  |  |

| 20  | CSI0_PIXCLK_OUT   | Р    | Pixel clock                                        |  |  |

| 21  | CSI0_DAT19_OUT    | 0    | Data 19                                            |  |  |

| 22  | CSI0_RST_B_OUT    | 0    | Reset                                              |  |  |

| 23  | GND               | Р    | Ground                                             |  |  |

| 24  | CSI0_PWM_OUT      | 0    | PWM                                                |  |  |

110127-50001 (25)

## J45: MIPI Camera

Board connector: 2x12 shrouded header, 2.00 mm, Samtec STMM-112-02-T-D-SM

Mating connector: Samtec TCSD series IDC cable assembly socket

The CPU-301-16 Development Kit includes a two lane Mobile Industry Processor Interface (MIPI) Camera Serial Interface (CSI) on header J45.

| Pin | Name          | Туре | Description                                        |

|-----|---------------|------|----------------------------------------------------|

| 1   | V_2P8V_SW     | PO   | Switched 2.8V                                      |

| 2   | V_1P5V_SW     | PO   | Switched 1.5V                                      |

| 3   | GND           | Р    | Ground                                             |

| 4   | V_1P8V_SW     | PO   | Switched 1.8V                                      |

| 5   | CSI_D0P_OUT   | 0    | Data 0 positive                                    |

| 6   | V_3P3V_SW     | PO   | Switched 3.3V                                      |

| 7   | CSI_D0M_OUT   | 0    | Data 0 negative                                    |

| 8   | CSI_SCL_OUT   | 0    | I <sup>2</sup> C clock                             |

|     |               |      | (Connects to general-purpose I <sup>2</sup> C bus) |

| 9   | GND           | Р    | Ground                                             |

| 10  | CSI_SDA_OUT   | Ю    | I <sup>2</sup> C data                              |

|     |               |      | (Connects to general-purpose I <sup>2</sup> C bus) |

| 11  | CSI_D1P_OUT   | 0    | Data 1 positive                                    |

| 12  | GND           | Р    | Ground                                             |

| 13  | CSI_D1M_OUT   | 0    | Data 1 negative                                    |

| 14  | CSI_RST_B_OUT | 0    | Reset                                              |

| 15  | GND           | Р    | Ground                                             |

| 16  | CSI_PWM_OUT   | 0    | PWM                                                |

| 17  | CSI_CLK0P_OUT | 0    | Clock positive                                     |

| 18  | GND           | Р    | Ground                                             |

| 19  | CSI_CLK0M_OUT | 0    | Clock negative                                     |

| 20  | NC            |      |                                                    |

| 21  | NC            |      |                                                    |

| 22  | NC            |      |                                                    |

| 23  | GND           | Р    | Ground                                             |

| 24  | NC            |      |                                                    |

## J46: Backlight 2

Board connector: 7-pin header, 1.25 mm, Molex 53261-0771

Mating connector: Molex 51021-0700 crimp housing

Header J46 provides the signals to control a backlight.

| Pin | Name    | Туре | Description                         |  |  |  |

|-----|---------|------|-------------------------------------|--|--|--|

| 1   | V_BL2   | PO   | Backlight power (12 V nominal)      |  |  |  |

| 2   | V_BL2   | PO   | Backlight power (12 V nominal)      |  |  |  |

| 3   | GND     | Р    | Ground                              |  |  |  |

| 4   | GND     | Р    | Ground                              |  |  |  |

| 5   | nBL2_ON | 0    | Turns backlight on or off           |  |  |  |

| 6   | BL_PWM0 | 0    | Controls intensity of the backlight |  |  |  |

| 7   | GND     | Р    | Ground                              |  |  |  |

110127-50001

## J47: MIPI Display

Board connector: 2x12 shrouded header, 2.00 mm, Samtec STMM-112-02-T-D-SM

Mating connector: Samtec TCSD series IDC cable assembly socket

The CPU-301-16 Development Kit provides a Mobile Industry Processor Interface (MIPI) Display Serial Interface (DSI) on header J47 supporting displays in handheld or mobile devices.

| Pin | Name           | Туре | Description                                        |

|-----|----------------|------|----------------------------------------------------|

| 1   | V_5V_SW        | PO   | Switched 5V                                        |

| 2   | V_3P3V_SW      | PO   | Switched 3.3V                                      |

| 3   | GND            | Р    | Ground                                             |

| 4   | NC             |      |                                                    |

| 5   | DSI_D0P_OUT    | 0    | Data 0 positive                                    |

| 6   | GND            | Р    | Ground                                             |

| 7   | DSI_D0M_OUT    | 0    | Data 0 negative                                    |

| 8   | DSI_SCL_OUT    | 0    | I <sup>2</sup> C clock                             |

|     |                |      | (Connects to general-purpose I <sup>2</sup> C bus) |

| 9   | GND            | Р    | Ground                                             |

| 10  | DSI_SDA_OUT    | IO   | I <sup>2</sup> C data                              |

|     |                |      | (Connects to general-purpose I <sup>2</sup> C bus) |

| 11  | DSI_D1P_OUT    | 0    | Data 1 positive                                    |

| 12  | GND            | Р    | Ground                                             |

| 13  | DSI_D1M_OUT    | 0    | Data 1 negative                                    |

| 14  | DSI_RST_B_OUT  | 0    | Reset                                              |

| 15  | GND            | Р    | Ground                                             |

| 16  | DSI_PWR_EN_OUT | 0    | Power enable                                       |

| 17  | DSI_CLK0P_OUT  | 0    | Clock positive                                     |

| 18  | NC             |      |                                                    |

| 19  | DSI_CLK0M_OUT  | 0    | Clock negative                                     |

| 20  | GND            | Р    | Ground                                             |

| 21  | GND            | Р    | Ground                                             |

| 22  | NC             |      |                                                    |

| 23  | NC             |      |                                                    |

| 24  | NC             |      |                                                    |

## J48: USB Host 3 (Option)

Board connector: 1x4 shrouded header, 1.25 mm, Molex 53398-0471

Mating connector: housing, Molex 51021-0400

As an option, header J48 can be populated to provide connection to USB Host 3.

| Pin | Name           | Туре | Description         |

|-----|----------------|------|---------------------|

| 1   | GND            | Р    | Ground              |

| 2   | HUB3_USB_P_OUT | IO   | USB Host 3          |

| 3   | HUB3_USB_N_OUT |      |                     |

| 4   | V_5V_HOST3     | PO   | 5 V DC power output |

## J49: HDMI Display

Board connector: HDMI Micro socket, Molex 46765-2001

Mating connector: HDMI Micro cable assembly

Micro socket J49 provides a standard Micro HDMI connection.

110127-50001 (27)

## J50: USB Host 1 (Alternate)

Board connector: 1x4 shrouded header, 1.25 mm, Molex 53398-0471

Mating connector: housing, Molex 51021-0400

In addition to USB socket J3, page 16, USB Host 1 is available on header J50.

| Pin | Name           | Туре | Description         |

|-----|----------------|------|---------------------|

| 1   | GND            | P    | Ground              |

| 2   | HUB1_USB_P_OUT | IO   | USB Host 1          |

| 3   | HUB1_USB_N_OUT |      |                     |

| 4   | V_5V_HOST1     | PO   | 5 V DC power output |

## J51: USB Host 2 (Option)

Board connector: 1x4 shrouded header, 1.25 mm, Molex 53398-0471

Mating connector: housing, Molex 51021-0400

As an option, header J51 can be populated to provide connection to USB Host 2.

| Pin | Name           | Туре | Description         |

|-----|----------------|------|---------------------|

| 1   | GND            | Р    | Ground              |

| 2   | HUB2_USB_P_OUT | IO   | USB Host 2          |

| 3   | HUB2_USB_N_OUT |      |                     |

| 4   | V_5V_HOST2     | PO   | 5 V DC power output |

110127-50001

# **System Specifications**

## **Power Supply**

The CPU-301-16 Development Kit accepts input power on header J27, page 20.

| Symbol           | Parameter      | Min | Тур. | Max | Units |

|------------------|----------------|-----|------|-----|-------|

| AC Power Adapter |                |     |      |     |       |

| V <sub>out</sub> | Supply voltage | 6   | 12   | 18  | V     |

| l <sub>out</sub> |                |     | 0.6  |     | Α     |

## **Electrical**

This section provides electrical specifications for the CPU-301-16 Development Kit.

#### **GPIO Header**

| Symbol                   | Parameter                               | Min | Тур. | Max  | Units |  |  |

|--------------------------|-----------------------------------------|-----|------|------|-------|--|--|

| USR_SCL_OUT,             | USR_SDA_OUT                             |     |      |      |       |  |  |

| F <sub>USR_SCL_OUT</sub> | Bus clock                               |     | 100  | 400  | kHz   |  |  |

| R <sub>PU</sub>          | Pull-up resistance (note 5)             |     | 10   |      | kΩ    |  |  |

| <b>V</b> <sub>PU</sub>   | Pull-up resistance (note 5)             |     |      | 3.3  | V     |  |  |

| SPI bus, USR_G           | SPI bus, USR_GPIO_x_OUT (note 6)        |     |      |      |       |  |  |

| V <sub>IH</sub>          | High-level input voltage                | 2.3 |      | 3.3  | V     |  |  |

| V <sub>IL</sub>          | Low-level input voltage                 | 0   |      | 1    | V     |  |  |

| V <sub>OH</sub>          | High-level output voltage IOH = -1 mA   | 3.2 |      |      | V     |  |  |

| V <sub>OL</sub>          | Low-level output voltage<br>IOL = 1 mA  |     |      | 0.15 | V     |  |  |

| R <sub>DRV</sub>         | Output driver impedance<br>Single-ended |     | 50   |      | Ω     |  |  |

#### Notes:

- 5. Pull-up resistors included on module.